MPS 专为 Xilinx Zynq UltraScale+ RFSoC 打造的一款小型超低噪音电源模块

作者:Heng Yang, Ph.D., Sr. Applications Engineer MPS

随着高性能FPGAs和ASIC的快速普及,电源模块设计也迎来了一定的挑战 —— 应用需要更宽的无线网络带宽来驱动,而数据中心则需要更高的功率密度、更快的负载瞬态响应和更高效的工作效率。AMD Xilinx Zynq UltraScale+ RFSoCs 即将多千兆采样 RF 数据变换器和软判决正向纠错(SD-FEC)集成到 SoC 架构中。新的系列产品配备了 ARM Cortex-A53 处理子系统,UltraScale+ 可编程逻辑以及 Zynq UltraScale+ 元器件中的最高信号处理带宽,为无线,有线接入,测试和测量,早期预警/雷达和其他高性能RF应用提供了全面的RF信号链。然而,更高集成度的 Zynq UltraScale + RFSoC 给电源解决方案设计也带来了挑战。此外,RF 数据变换器的性能与其电源的噪声水平紧密相关。MPS 电源模块既具有很高的工作效率还能最大限度地减少电路板的使用面积。此应用说明概括了AMD Xilinx Zynq UltraScale+ RFSoC 电源设计解决方案。演示的 EVREF0102A 参考设计电源为 RF 数据变换器提供了超低噪声电压。

电源架构

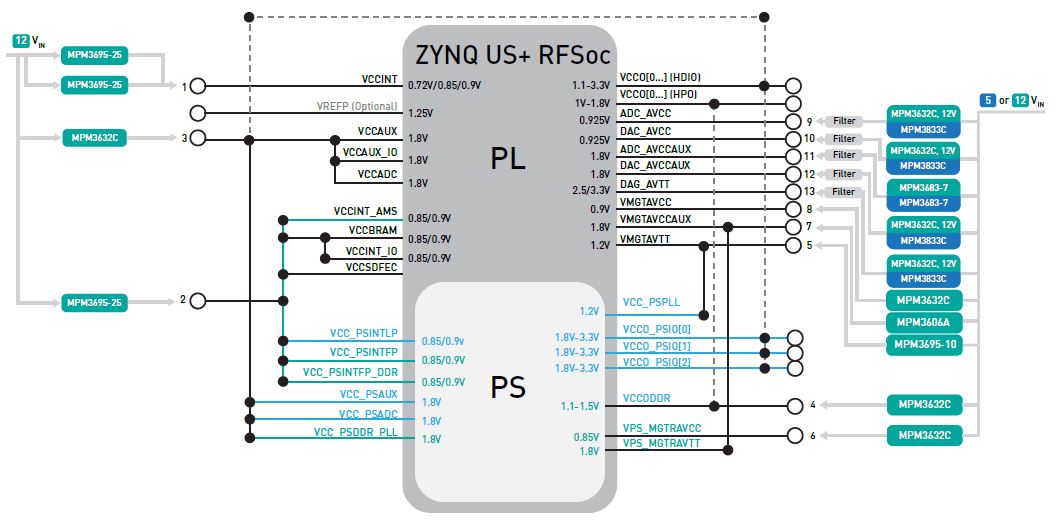

图 1中展示了 Zynq UltraScale+ RFSoC 的电源架构图。正如图中所示,RFSoC 需要30多个电压轨。PL 域中的电压轨用于RFSoC,PS域中的电压轨用于内置ARM内核。合并电压轨可以最大限度地减少变换器的使用数量。MPS电源模块可以最大限度地降低 PCB 占板面积,简化电源设计。

图 1. MPS 为 Zynq UltraScale+ RFSoC 设计的电源解决方案

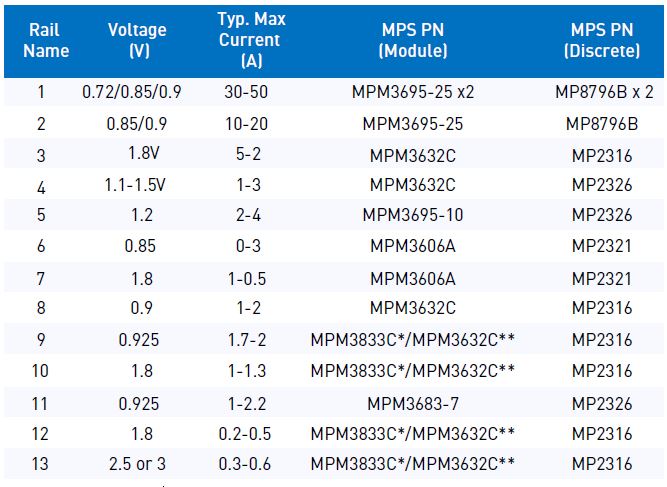

每个电压轨的电流规格取决于在 RFSoC 上运行的产品和具体应用/程序。 表 1 列出了 Zynq UltraScale+ RFSoC 系列产品每根电压轨的典型电流要求。建议使用 AMD Xilinx 电源评估 (XPE) 工具 来评估精确的电流要求以便优化电源解决方案。除了电压和电流规格,AMD Xilinx FPGA 电压轨的供电电源必须符合以下要求:

- 稳态下所有电压轨(除了模拟电压轨之外)的输出电压纹波必须低小于10mV。

- 所有电压轨的启动必须为单调上升。

- 在电流上升速率为100A/μs,负载瞬态为 25% 时,核心电压轨(VCCINT) 的输出电压偏差必须小于 +- 3%。

- 供电电源的上下电时序必须遵循 AMD Xilinx 定义的特定时序。

*支持高达 6V 的输入电压, **支持 12V 输入电压。点击查看整套分立解决方案。

表 1. MPS 设计用于AMD Xilinx Zynq UltraScale+FSoC 的电源模块解决方案

使用电源模块优化电源解决方案

MPS 电源模块提供了高度集成的高效电源解决方案。图 2 展示了 MPS 电源模块的典型结构,它在单个封装内集成了 MPS 单片 IC、电感和选定的无源元件。采用 Mesh-connect 封装技术,将器件贴装在引线框架上可以最大限度地减少功率 IC/电感与 PCB 板之间的热阻。单片 IC 将功率 FET、控制电路和驱动集成在一个单独的硅片中。单片技术可以最大限度地减少驱动电路和功率 FET 栅极之间的寄生电阻。从而能最大限度地减少开关损耗。

表 1显示了 MPS 为 AMD Xilinx Zynq UltraScale+FSoC 设计的电源模块解决方案。备注,MPS同时也提供分立式电源解决方案。

图 2. MPS 电源模块典型结构

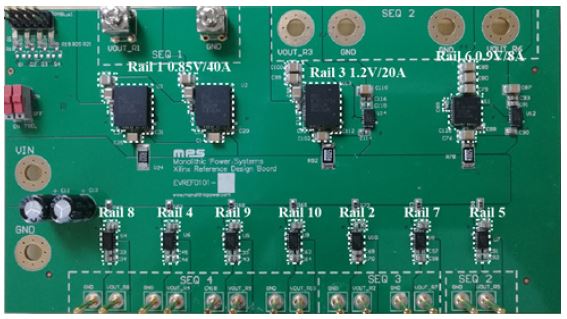

图. 3 演示了用于AMD Xilinx Zynq UltraScale+ RFSoC的参考设计板 (不含 RF 数据变换器电压轨)。参考设计板使用了 5 款出色的电源模块。 MPM3695-25 是一款 16V,20A 电源模块。核心电压轨采用 2 个并联的 MPM3695-25s 以提供高达 50A 的峰值电流。单个 MPM3695-25 为电压轨 2 提供高达 25A 的峰值电流。MPM3695-10 是一款 14V,7A 超薄电源模块。 MPM3632C是一款 18V,3A 强制连续导通模式(CCM)电源模块。

图 3. Zynq UltraScale+RFSoC 参考设计板

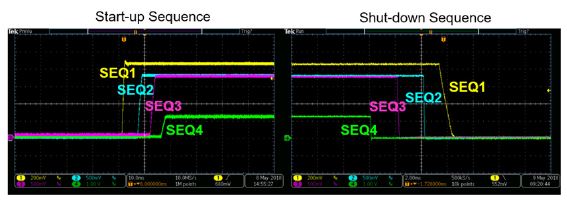

图 4.上下电时序

MPM3606A是一款 21V, 0.6A 电源模块。同一系列还提供了兼容引脚的 1A,2A 和 3A 电源模块,让电源解决方案设计更加灵活。 经充分验证,参考设计的性能符合 AMD Xilinx 要求。 图 4 显示了上下电时序波形图。

集成电感的 MPM3695 先进电源模块系列为 FPGAs 和 ASICs 供电方案提供了通用的解决方案。MPM3695 系列产品可通过堆叠多个 MPM3695-25s 或 MPM3695-10s 扩展输出电流。相比分立式负载点(POL)解决方案,MPM3695 系列产品可以提供高达 60% 的高功率密度,不仅简化了 PCB 的布局和功率级设计,还能最大限度地减少外部元器件以及电源变换器专有知识的使用,大大优化了补偿网络设计。通过采用单片电源IC结构和定制集成电感设计,同时结合卓越的封装技术,MPM3695 系列电源模块的封装尺寸比竞争者足足缩小了40%。

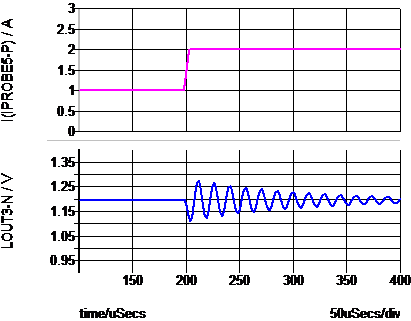

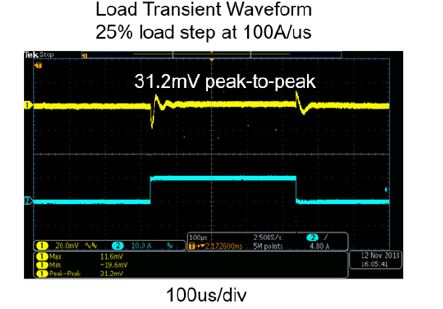

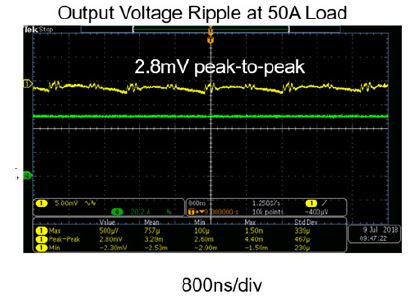

图 5 和 6 分别展示了电流上升速率为 100μA/s,负载瞬态为 25% 时的负载瞬态波形图以及满载下的输出电压波形图。如图所示,负载瞬态期间的输出电压偏差小于 ± 3%,并且在稳态下输出电压纹波小于 10mV。

图 5. 核心电压轨的负载瞬态纹波。

图 6. 核心电压轨的输出电压纹波。

专为赛灵思 ZCU1275 设计平台开发的模拟电源模块

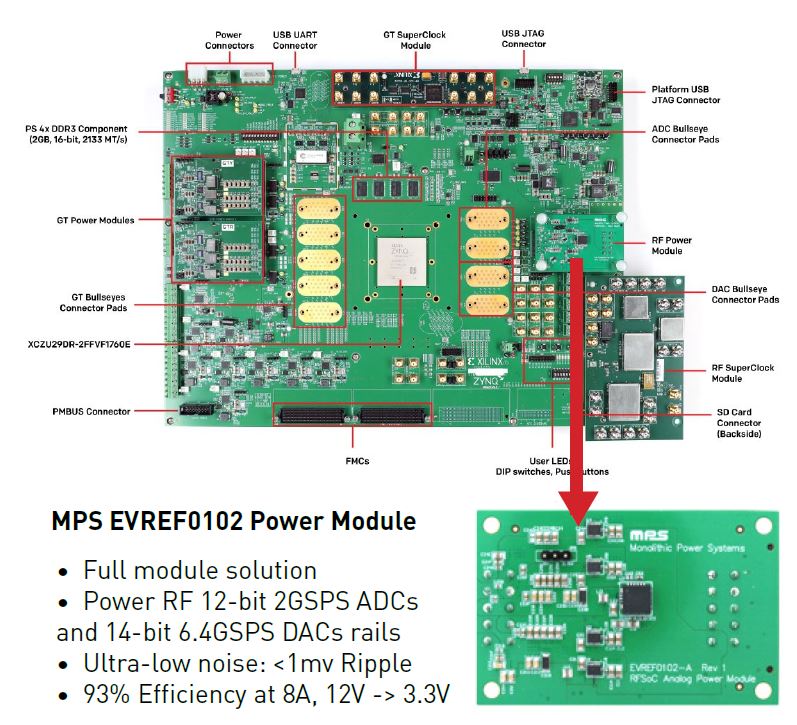

AMD Xilinx Ultrascale+ RFSoC 内置了一个高速模数转换器(ADC)和一个数模转换器(DAC),要求超低的输出噪声。与传统低压差(LDO)稳压器相比,开关电源(SMPS)的高效优势显而易见。但也因其开关特性,开关电源在开关频率和谐波处会产生噪声。MPS电源模块为两个非常敏感的ADC和DAC电源采用了两级CLC无源滤波器,最大限度地降低了输出电压噪音。EVREF0102A是专为赛灵思ZCU1275 Zynq UltraScale+RFSOC 设计平台所开发的模拟电源模块。图 7 演示了EVREF0102电源模块。

图 7. EVRF0102 超低噪音电源模块

针对所有敏感型 RF 数据变换器电压轨,其输出电压均小于1mV。EVREF0102A采用了五个带集成电感器的高效降压开关电源模块。 MPM3833C是一款6V、3A、超小型降压电源模块, MPM 3683-7是一款16V、8A电源模块。 两款电源模块都具有集成保护功能,包括OCP、OVP、UVP和OTP。与传统的LDO解决方案相比,EVREF0102A的效率提高了80%。EVREF0102A模拟电源模块通过采用强制连续导通工作模式(CCM)和后无源滤波器,实现了超低噪声水平,可以满足AMD Xilinx对高速数模变换器规范。其中,两个最敏感的ADC和DAC电源使用CLC无源滤波器,其他电源使用电容滤波器。请见附录参考设计。

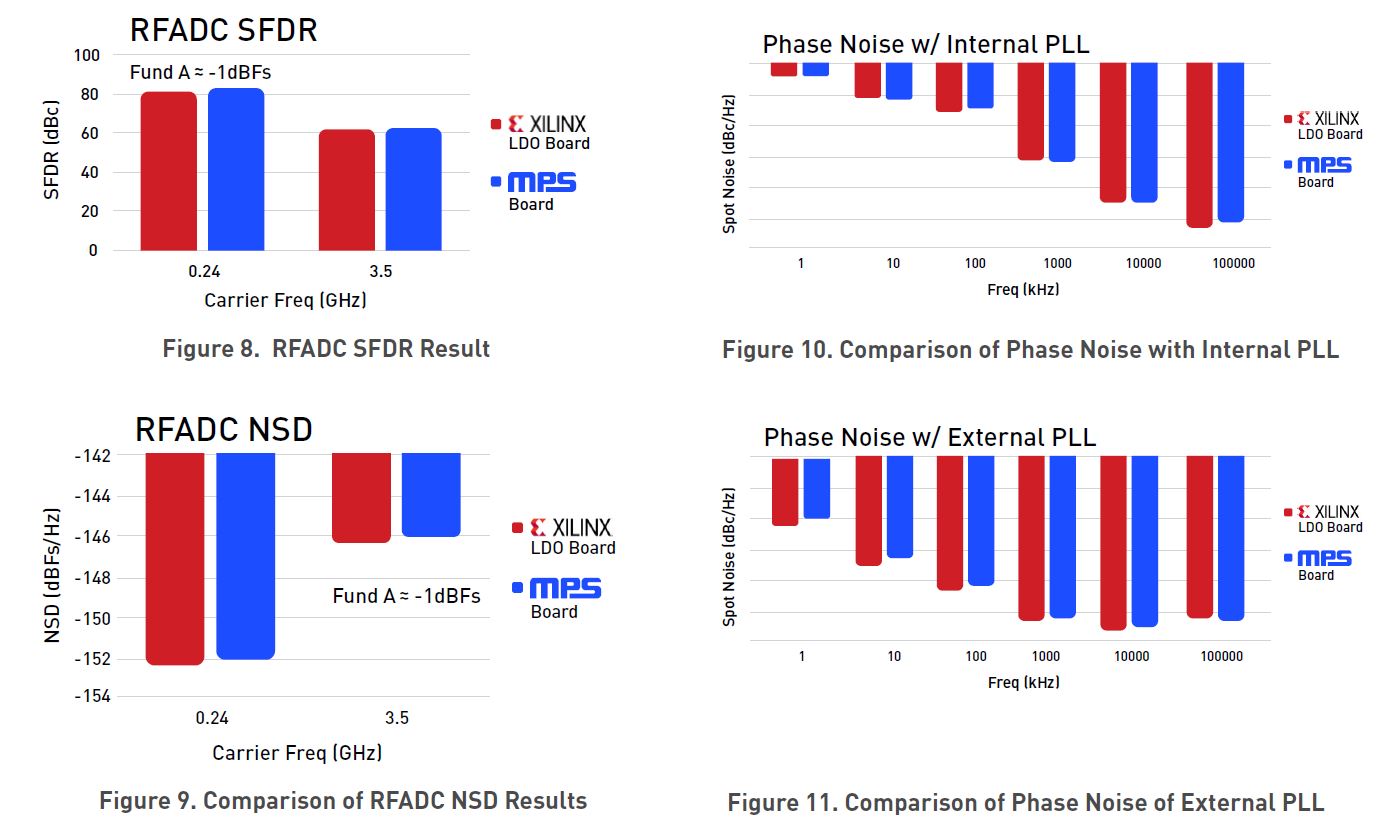

图 8-11 为传统LDO解决方案与MPS电源模块对照图。在赛灵思实验室里,ZCU1275开发板收集到了实验结果。如图中所示,MPS电源模块与传统LDO解决方案的噪音水平相当。

结论

用于AMD Xilinx FPGAs的MPS电源模块解决方案具有高效率、全集成和尺寸小特性。可扩展电源模块为核心电压轨提供了通用解决方案。对于敏感型的RF数据变换器电压轨来说,采用电源模块代替传统LDO可以显著提高效率。MPS提供的2个参考设计板性能已充分验证。本应用说明的附录中概述了用于RF数据变换器电压轨的无源滤波器设计工艺,该滤波器可以最大限度地降低输出电压纹波。

附录: 两级滤波器设计

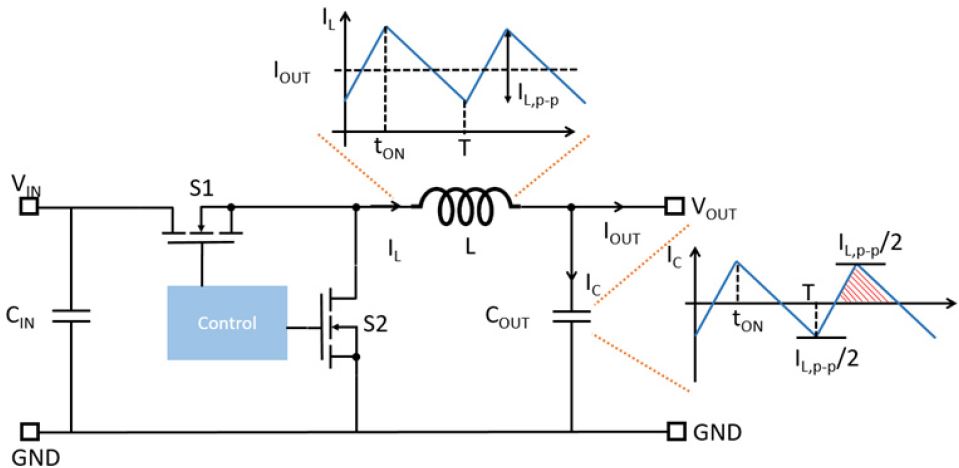

同步降压变换器由输入电容器CIN、两个开关(S1和S2)及其体二极管、储能电感(L)和输出电容器(COUT)组成。当S1接通,S2断开时,输入源向功率电感(L)和负载提供电流。此时,电感电流上升。当S2接通而S1断开时,电感器中存储的能量被转至输出电容器和负载,导致电感器电流下降。降压调节器的开关行为导致输出电压波动。应在输出端放置一个输出电容器(Cout),以便在稳态时平滑输出电压。输出电容器通过为高频电压分量提供低阻抗路径,将高频纹波反射回接地,从而降低输出电压纹波。

图 1: 低噪音滤波器设计

接着,假设Buck降压变换器采用连续导通模式(CCM),以最大限度地降低输出电压纹波。L电感值也满足电感器的电流纹波要求。其最小值可通过以下公式计算得出:

其中,VIN 和 VOUT 分别代表输入和输出电压,D=VOUT/VIN 代表占空比, I_(L,p-p)代表电感的峰-峰电流纹波,fSW代表变换器的开关频率。通常,峰-峰电感电流纹波可设置为输出DC电流的20-40%。

输出电容值应能确保其输出纹波低于应用需要的峰-峰纹波值。对于单级电容滤波器,其最小输出电压纹波可达1~2 mV。

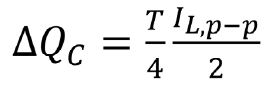

在稳态下的一个开关周期内,向电容器输送的净电荷为零。图 1阴影区的电容电荷可通过以下公式计算得出:

其中T为开关切换周期。根据定义,给定周期内的电容电荷也可表示为:

(3)

公式(2)代入公式(3),得到输出峰-峰电压纹波(VOUTp-p)所需的最小电容为:

理想情况下,并联更多的输出电容可以降低对地的高频阻抗,从而减小输出纹波。而实际上,输出电容器是横放在印刷电路板上的。如果在印刷电路板上增加更多的输出电容,会给并联电路增加额外的寄生电感和交流电阻,增加输出电容的效果会逐渐降低。

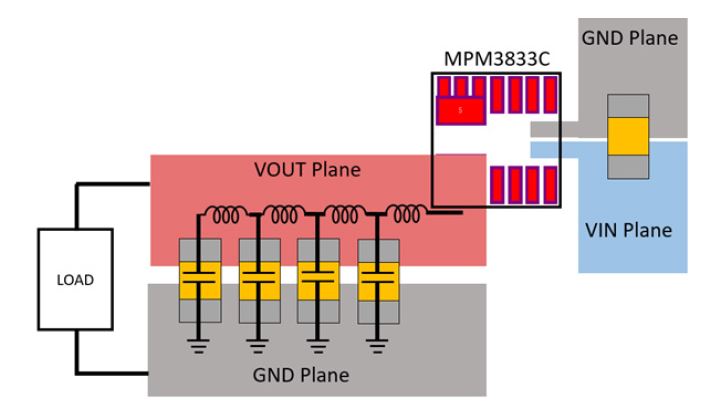

如图 2所示的典型PCB布局,MPS电源模块通过集成电感,可大大简化电源转换器设计。在MPM3833C的PCB布局中,为输出功率路径进行了大面积铺铜,这能最大限度地降低功率损耗。输出电容器也是沿着输出电流路径放置的。如图所示,随着放置在输出平面上的电容器越来越多,附加电容器与电源模块输出引脚之间的距离也变得越来越大。因此,在离电源模块较远的输出电容中,会产生更多的寄生电感。增加输出电容的效果变得越来越差,最终远端电容的高频对地回路以寄生电感为主。

图 2. MPM3833C电源模块典型PCB布局

为演示回路寄生电感的影响,这里使用Simplis设计出了具有不同输出电容的MPM3833C。并假设每个增加的输出电容向回路引入0.5nH的寄生电感。图 3展示了带有一个22µF电容器的电源模块输出纹波。可以看出,输出电容器的确有效地降低了输出纹波:在5V输入,1.2V 输出和2A负载时,输出纹波降至约为3mV。

图3带一个22µF输出电容的MPM3833C所产生的输出纹波

为了进一步降低输出电压纹波,可以在输出端再增加一个22µF的输出电容。由于新增的电容器必须放置在离电源模块更远的地方,因此新增电容器所引入的寄生电感为1nH。 图 4 (a) 给出了仿真输出电压波形图,其中输出电压纹波已降到2mV。与图 3所示的波形图相比,增加一个22μF输出电容器可将输出电压纹波有效降至3mV,而再增加一个 22μF电容器的效果其实并不明显。图 4(b)显示了多一个22μF电容器后(总共4x22μF)的输出电压纹波。最后一个22µF 电容器在其高频对地回路中引入的寄生电感为1.5nH。如图所示,与使用3x22µF的情况相比,多增加一个电容器后输出纹波降低度小于5%。

图4带(a) 4x22uF和(b) 5x22uF输出电容的MPM3833C所产生的输出纹波

从图3和图4的演示可知,PCB上添加的电容器越多,PCB铺铜/走线所产生的寄生电感就越多。最终,增加更多电容器的作用被回路中不断增加的附加寄生电感所抵消。

第二级滤波器设计

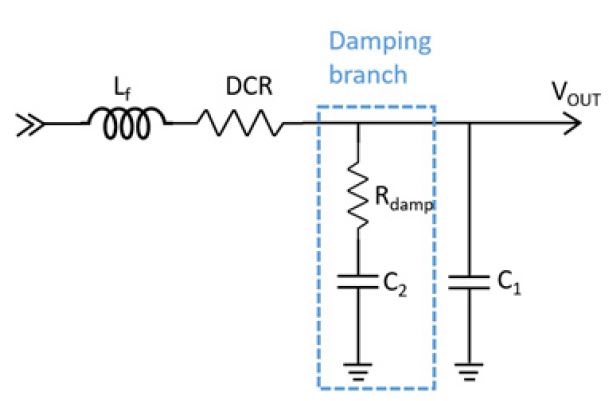

通常,并联输出电容器能将输出电压纹波有效降低到最低1-2mV。要实现低于1mV的纹波,需要一个第二级输出滤波器。图5展示了第二寄滤波器的典型电路。第二级滤波器由一个滤波电感及其串联电阻(DCR)、一个对地电容器支路和一个阻尼支路组成。滤波电感(Lf)在设计的高频范围内具有电阻,以热量的形式耗散噪声能量。该电感器与附加的并联电容器结合形成低通LC滤波器网络。

图5. 带并联阻尼支路的两级LC滤波器

合理设计的第二级滤波器会有效降低输出电压噪声。针对工作频率来选择LC滤波器组件至关重要。设计的第一步是根据公式(4)选择第一级输出电容器。在第一极的设计中,典型的输出电压纹波一般为5mV至10mV。所以,通常选用10-22μF电容器就足够了。为保证系统的稳定性,第一级的电容容量(COUT)必须小于第二级的旁路电容(C1)。

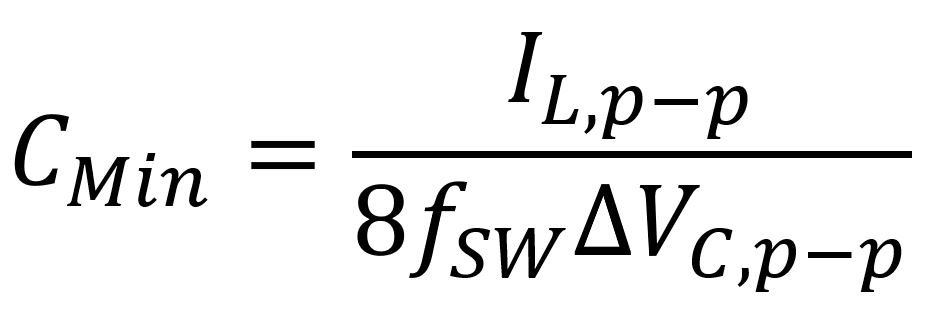

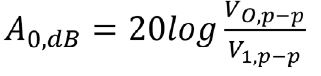

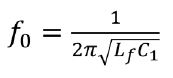

一旦确定了第一级电容器并给出了规定的输出电压纹波(在给定频率下),第二级LC滤波器所需的衰减可确定为:

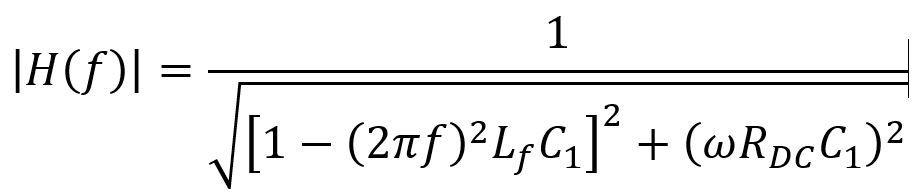

其中,V1,p--p 代表输出电容器的峰-峰电压纹波,V0,p-p 代表输出电压的峰-峰电压(在第二级滤波器之后)。使用相量分析,LC滤波器增益的振幅可通过以下公式计算:

阻尼支路(由一个大型电阻和电容串联组成)的阻抗在开关频率下比对地支路大得多。因此,在下面的分析中,图 5 所示的滤波器可等效于一个二阶RLC滤波器。滤波器的截止频率为:

通常,可以选择电感值为0.22µH到1µH的电感器来实现所需的输出纹波。此滤波电感的并联阻抗会增加功耗并降低了输出电压的精度,因此应选择DCR最小的电感。需要注意的是,随着直流电流的增大,电感的磁芯材料会逐渐饱和,从而也会降低电感的电感值。

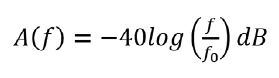

一旦选择了滤波电感器,就可以从数据表中提取其DCR。第二级LC滤波器是一个二阶滤波器,在截止频率之后每十档衰减40db。给定频率下的衰减可根据以下公式估算出:

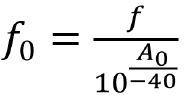

根据公式(5)计算出的衰减,可使用以下公式计算出所需的截止频率:

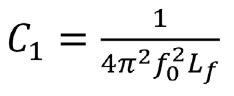

然后,可计算出所需的对地支路的电容值(C1):

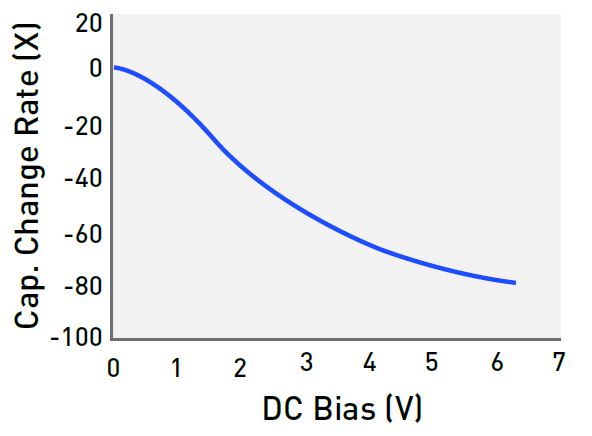

由于低ESR和ESL,应使用陶瓷电容器作为旁路电容器。 需注意,在直流偏压下,陶瓷电容器的电容会发生显著降额。图6给出了额定电压为6.3V的Murata 0805陶瓷电容器的直流降额曲线。如图所示,在满额直流偏压下,电容降到额定值的20%。旁路电容器应在额定直流偏压下选择,以便考虑降额值。

图 6. DC偏置下的典型陶瓷电容降额曲线

阻尼

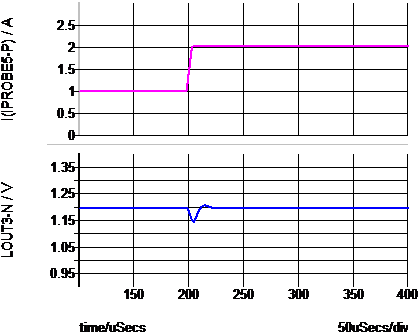

如果第二级LC滤波器的阻尼不合适,可能会出现谐振。滤波电感与对地支路之间的谐振会放大输出纹波,在负载瞬态时还会产生不希望出现的振铃。图7 (a) 显示了带第二级LC滤波器的欠阻尼变换器系统的输出电压。最初,系统在稳态下运行。当t=200µs时,负载瞬态从1A变成2A,输出电压引起振铃。图7b(b)说明了过阻尼二级滤波器负载瞬态下的输出电压和电流。为避免在负载瞬态时产生振铃,第二级LC滤波器谐振必须得到适当的抑制。在大多数设计中,第二级滤波器会被放置在控制回路之外,以避免控制回路不稳定。因此,阻尼必须使用无源元件(附加阻尼电阻)。

图 7. (a)欠阻尼LC滤波器和(b)过阻尼LC滤波器瞬态响应

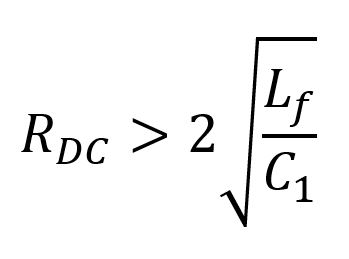

滤波电感通常包含与电感串联的寄生直流电阻。此DCR向网络提供阻尼。然而,为了能向串联RLC电路提供足够的阻尼,串联电阻必须满足

mps-xilinx-artcile-q1-2019-_1.pdf

_____________________________________

直接登录

创建新帐号