通过 SPICE 仿真中的寄生电感效应预测 VDS 开关尖峰

每月为您发送最具参考价值的行业文章

我们会保障您的隐私

简介

电源行业一直致力于为数据中心和5G等应用中的电源设备带来更高的电源转换效率和功率密度。与具有单独驱动器 IC 的传统分立 MOSFET 相比,将驱动器电路和功率 MOSFET(即DrMOS)集成到 IC 中可以实现更高的功率密度和效率。而且,DrMOS 的倒装芯片技术通过缩短响应时间并减小芯片与封装之间的电感,能够进一步优化稳压器的性能(见图 1)。

图 1:传统引线键合技术与倒装芯片技术

然而,由于寄生电感与 MOSFET 输出电容(COSS)之间的谐振特性,基板和 PCB 上的寄生电感会极大地影响漏源电压(VDS)尖峰。高 VDS尖峰可能会导致 MOSFET 雪崩,从而导致器件性能下降并带来可靠性问题。为了防止 MOSFET 发生雪崩击穿,需要通过一些方法来减轻电压应力。

第一种方法是在 DrMOS 上应用电压更高的双扩散 MOSFET (DMOS) 工艺。但如果在功率 MOSFET 设计中采用此工艺,由于同一空间内并联 DMOS 数量减少,DrMOS 的导通电阻(RDS(ON))会较高。

第二种方法是使用缓冲电路来抑制电压尖峰。但这种方法会导致缓冲电路产生额外的损耗。此外,添加缓冲电路可能无法有效地降低 MOSFET 的VDS尖峰,因为引起谐振行为的杂散电感主要集成在 DrMOS 封装中。

采用上述方法尝试提高稳压器效率并降低 MOSFET 电压尖峰,可能会导致难以量化和优化寄生电感对 PCB 和基板的影响。本文将首先讨论如何对寄生电感进行建模,然后在 SPICE 仿真工具中应用等效寄生电路模型来预测VDS开关尖峰。文章还将提供实验结果来验证寄生模型的可行性,并在最后深入分析如何对DrMOS上的寄生电感进行优化。

相关内容

-

文章

MPS 专为 Xilinx Zynq UltraScale+ RFSoC 打造的一款小型超低噪音电源模块

随着高性能FPGAs和ASIC的快速普及,电源模块设计也迎来了一定的挑战

-

视频

面向服务器应用的非隔离式、双两相降压 Intelli-Module:MPC22163-130

MPC22163-130 是一款 130A、非隔离式、双相降压处理器核心供电 Intelli-Module

-

应用

5G 电源解决方案

为了满足高功率和高效率的要求,MPS推出了5G供电解决方案

-

文章

分析和仿真PCB 交流电阻损耗,优化DrMOS核心电压

作为开关电源损耗的一部分,印刷电路板(PCB)主回路纹波电流阻抗的损耗常被忽略不计

DrMOS 上的寄生电感建模

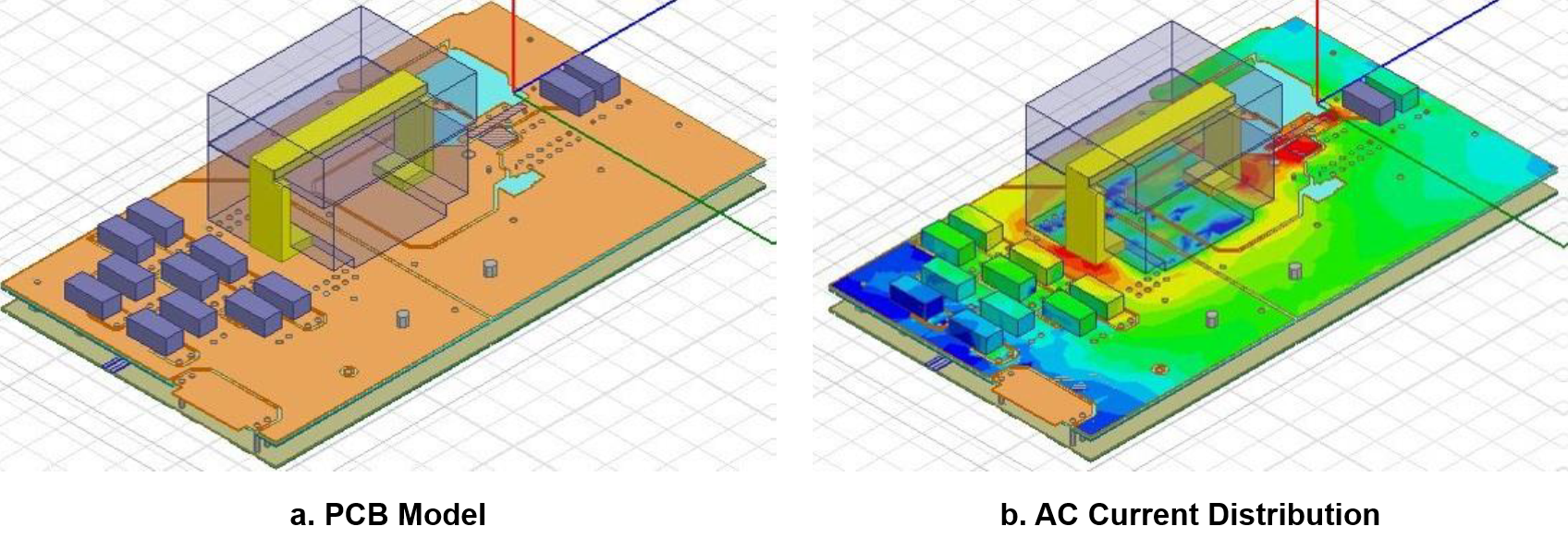

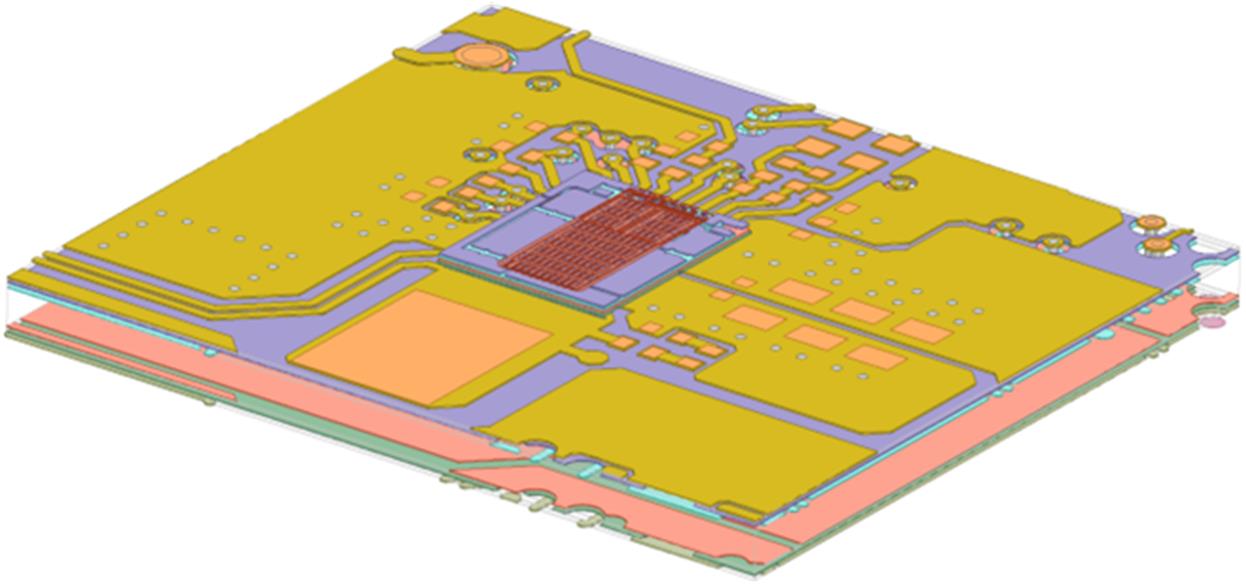

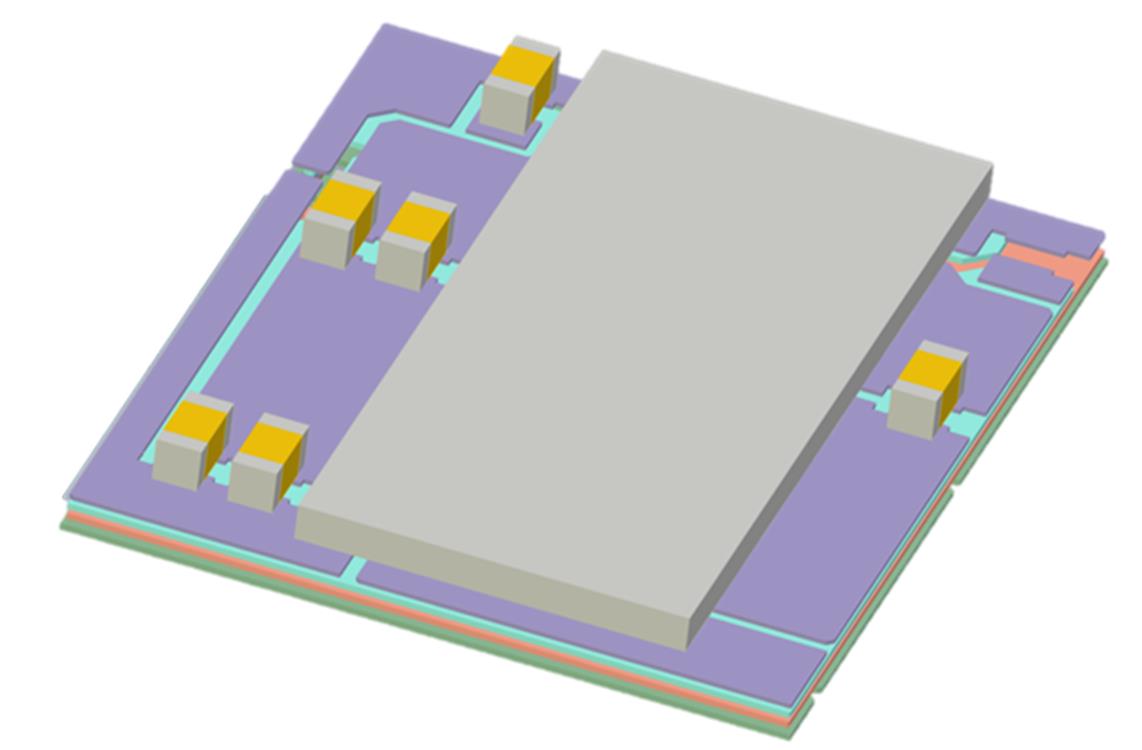

为了对寄生电感进行建模,我们构建 DrMOS 和 PCB 的 3D 结构来进行仿真分析(见图 2)。 材料、叠层信息以及 PCB 和封装层厚度等参数对于建模的准确性都非常重要。

对 PCB 和 DrMOS 进行 3D 建模之后,可以通过 ANSYS Q3D 对寄生电感进行表征和获取。本文重点关注 MOSFET 的 VDS尖峰,因此主要的仿真设置为电源网络和驱动器网络上的寄生参数。

图 2:DrMOS 和 PCB 的 3D 建模结构

当需要从 Q3D 获得寄生分量时,可以在不同频率条件下选择寄生电感矩阵(包括 DrMOS 上每个网络的自项和互项)。由于上管MOSFET(HS-FET)和下管MOSFET(LS-FET)上VDS的谐振频率在300MHz至500MHz之间,因此采用300MHz条件下的寄生电感矩阵进行进一步的行为模型仿真。

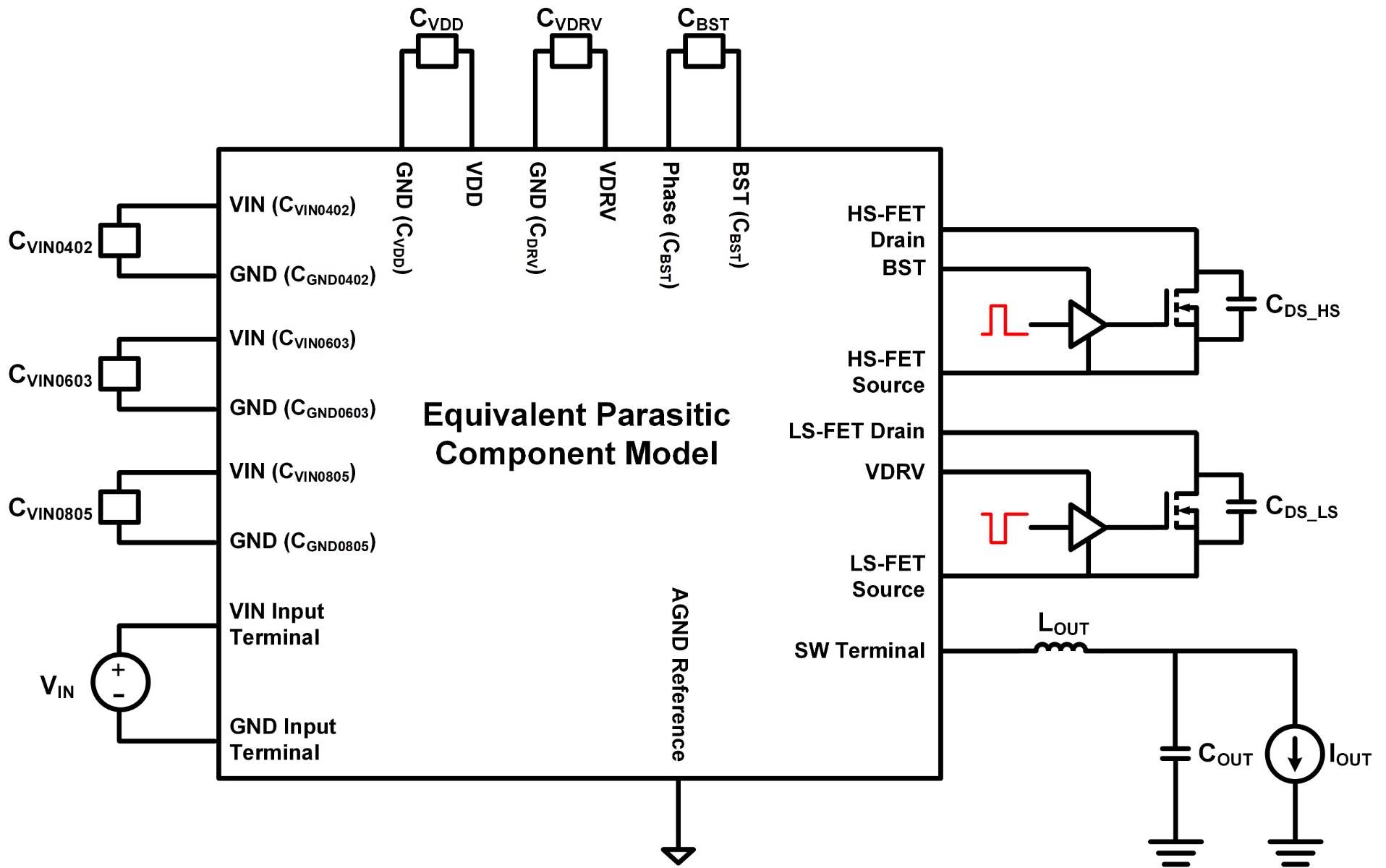

SPICE 上的行为模型仿真

从Q3D导出等效寄生元件模型后,就可以考虑不同类型的去耦电容对PCB的影响。由于在多层陶瓷电容 (MLCC) 上施加直流电压后电容会衰减,因此必须考虑每个 MLCC在特定直流电压偏置条件下的等效电路。而且每个考量因素都应基于 MLCC 的工作电压。 图 3 显示了 SPICE 上行为模型仿真的电路配置。

图3:行为模型仿真的电路配置

基于图 3 的原理图,仿真和测量条件如表1所示。

表1:仿真方案及实验测试台规格

| 参数 | 值 |

| 输入电压(VIN) | 12V |

| 输出电压(VOUT) | 1.8V |

| 开关频率(fSW) | 800kHz |

| 输出电感 | 100nH |

| 负载 | 50A |

| VDRV / VDD 电压 | 3.3V |

采用 MP87000-L 实现的 DrMOS 解决方案

MP87000-L是一款 90A 的单片半桥,它具有内置功率 MOSFET 和栅极驱动器,适用于服务器内核和显卡内核稳压器应用。为抑制电压振铃,MP87000-L 采用了Quiet SwitcherTM技术。该技术只能在单片架构中实现,它提高了器件可靠性,降低了 EMI,还降低了对 PCB 布局的敏感性。

MP87000-L 非常适合要求高效率和高功率密度的服务器应用,它采用 TLGA-41 (5mmx6mm) 封装。

采用 MP87000-L 在 LS-FET 上的VDS仿真和实验结果如图 4所示。

图 4:VDS (LS-FET)仿真和实验结果

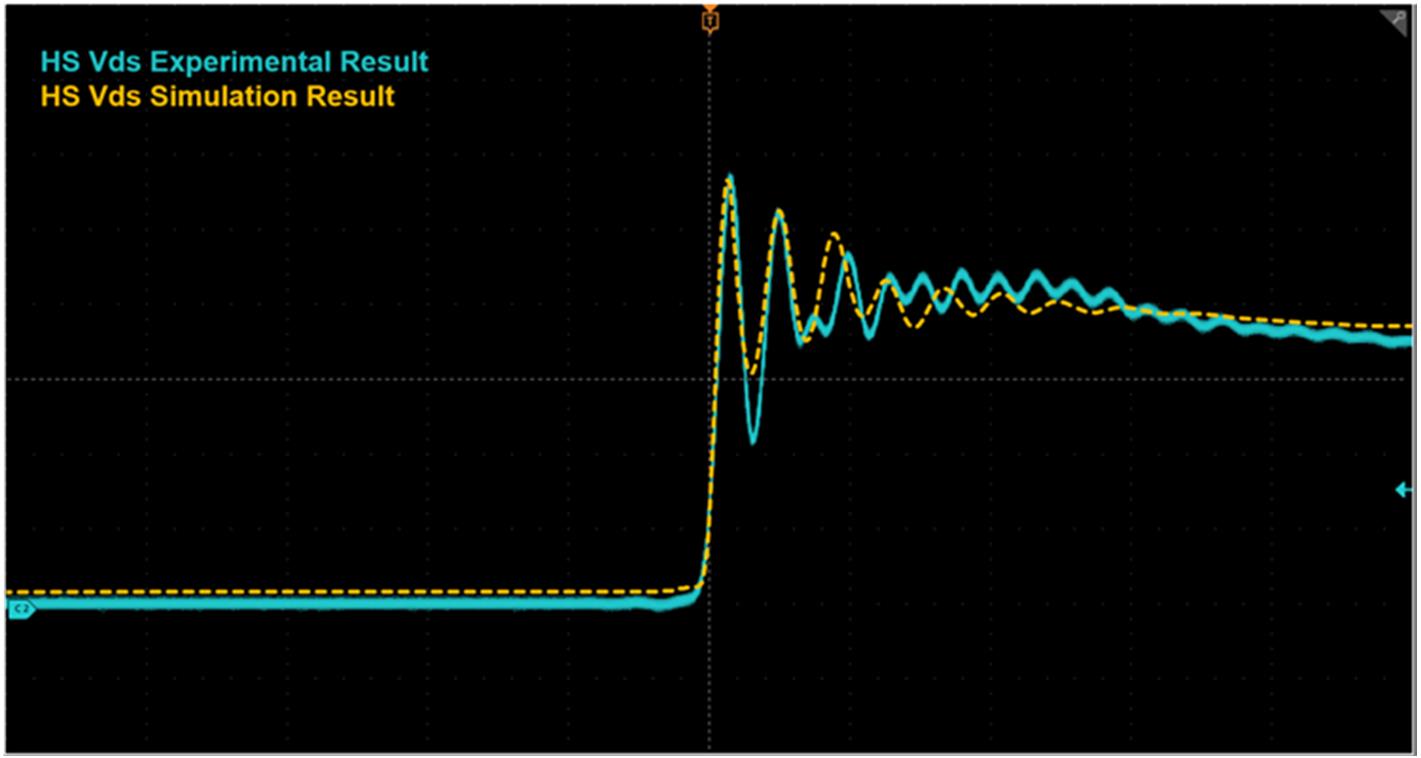

采用 MP87000-L 在 HS -FET 上的 VDS仿真和实验结果如图 5所示。

图 5:VDS (HS-FET)仿真和实验结果

从图 4 和图 5 可以看出,仿真结果中的 VDS 尖峰几乎等同于实验结果。在不同负载条件下的附加仿真和实验结果如表2所示。

表2:不同负载条件下的仿真和实验结果

| 负载 | 仿真 HS-FET VDS 尖峰 | 测量 HS-FET VDS 尖峰 | 仿真 LS-FET VDS 尖峰 | 测量 LS-FET VDS 尖峰 |

| 30A | 14.4V | 15.8V | 12.4V | 13.9V |

| 40A | 14.6V | 15.4V | 12.5V | 13.5V |

| 50A | 17.1V | 16.5V | 13.4V | 13.3V |

| 60A | 19.1V | 19.2V | 12.9V | 13.1V |

| 70A | 21.4V | 21.8V | 13.5V | 13V |

表 2 表明仿真 VDS 与测量结果一致。 也就是说,通过实施多种降低寄生电感的优化方法,行为模型仿真的 VDS 尖峰预测可以预见 MOSFET 上潜在的雪崩击穿。

优化寄生电感

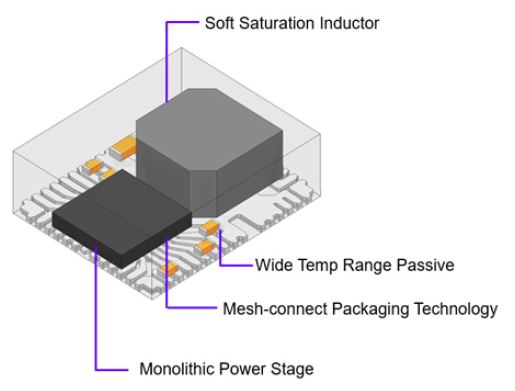

为了在不影响效率的情况下抑制 VDS 尖峰,优化 PCB 和封装中的寄生电感至关重要。我们可以借助先进的封装技术,将输入电容集成在封装中以缩短去耦路径(见图6)。 在封装内并联嵌入式电容可以有效降低DrMOS上的等效寄生电感。

图 6:带嵌入式电容的 DrMOS 结构

表 3 显示了在 MP87000-L 中使用不同去耦电容配置时的等效寄生电感和 VDS 尖峰。

表 3:不同电容配置下的等效寄生电感和 VDS 尖峰

| 电容配置 | 等效寄生电感 | 仿真 HS-FET VDS 尖峰(负载 = 50A) | 仿真 LS-FET VDS 尖峰(负载 = 50A) |

| 3个嵌入式电容, 2个PCB 0402电容, 3个 PCB 0805 电容 |

157pH | 17.1V | 13.4V |

| 2个嵌入式电容, 2个PCB 0402电容, 3个 PCB 0805 电容 |

180pH | 18.2V | 14.3V |

| 1个嵌入式电容, 2个PCB 0402电容, 3个 PCB 0805 电容 |

206pH | 21.5V | 16.9V |

| 2个PCB 0402电容, 3个 PCB 0805 电容 |

285pH | 27.7V | 20.6V |

从表3的仿真结果来看,不仅等效寄生电感降低了, MOSFET上的 VDS 尖峰也得到抑制。而且,由于 MLCC 的低 ESR 特性,嵌入式输入电容不会产生额外的功率损耗。因此,添加不同的嵌入式输入电容可以减少 DrMOS 应用中的寄生电感。

结语

本文阐述了寄生电感对 VDS 开关尖峰的影响,探讨了防止 VDS 开关尖峰导致 MOSFET 雪崩击穿的几种方法。

为了量化寄生电感对 VDS 开关尖峰的影响,本文首先对寄生电感进行建模,然后提出了SPICE 上的行为建模。通过 SPICE 获得的仿真结果与MP87000-L等DrMOS解决方案的实验结果极为吻合,这意味着该行为模型可以准确预测 MOSFET 雪崩击穿的风险。

为了有效抑制 VDS尖峰而不用考虑任何权衡,可以在封装中引入嵌入式电容。行为模型仿真证实,嵌入式电容可以降低等效寄生电感,从而降低 VDS 尖峰,同时不会产生额外损耗。MPS 提供丰富的 48V 电源模块、降压变换器和处理器核心电源控制器系列产品,可以助您完善数据中心解决方案。

_______________________

您感兴趣吗? 点击订阅,我们将每月为您发送最具价值的资讯!

技术论坛

Latest activity 4 months ago

Latest activity 4 months ago

11 回复

11 回复

Latest activity 2 months ago

Latest activity 2 months ago

24 回复

24 回复

Latest activity 2 months ago

Latest activity 2 months ago

17 回复

17 回复

直接登录

创建新帐号