利用双输出电源模块实现 FPGA 供电

每月为您发送最具参考价值的行业文章

我们会保障您的隐私

简介

电信系统、数据存储和现场可编程门阵列 (FPGA) 的需求增长让电力输送变得越来越复杂,也对电源,特别是电压稳压器(VR)提出了更高的要求。大多数 VR 应用领域都需要在效率、I/O 电压范围、电压容差和尺寸之间做出权衡。在提供精确电压控制的同时满足 FPGA 电源轨的需求非常重要。

随着电源轨数量的不断增加,设计人员必须找到同时适用于大电流和小电流的电源轨解决方案。多相电源能够实现更高电流传输,同时降低电感尺寸要求,而多输出电源则允许设计人员通过单个 IC 为多个 FPGA 轨供电。这让设计人员能够在满足所有现代电力输送要求的同时,减少占板空间并简化设计。

本文将以双输出电源模块MPM54322为例,探讨如何利用多输出电源来满足 FPGA 的电源轨需求。实现FPGA 供电的关键考量因素包括电压轨调节,以及 FPGA 电源轨的正确启动与安全关断。

FPGA 电压轨调节

负载瞬变和电压纹波

FPGA系统通常需要很多电源轨,且电压和电流要求各不相同。根据功能的不同,高级 FPGA 设计通常需要多达 8 个电源轨,例如双倍数据速率 (DDR) 内存、高速收发器以及其他外围设备。大多数基于 FPGA 的系统都采用 12V 总线供电,不同 FPGA 电源轨所需的电压在 0.65V 和 3.3V 之间变化。

电压纹波容差是电源设计的主要指标,也是 FPGA 供电需满足的最严格规范之一。制造商的数据表中会列出该容差值;通常情况下,电压纹波容差不得超过额定电压的 ±3% 或 ±30mV。

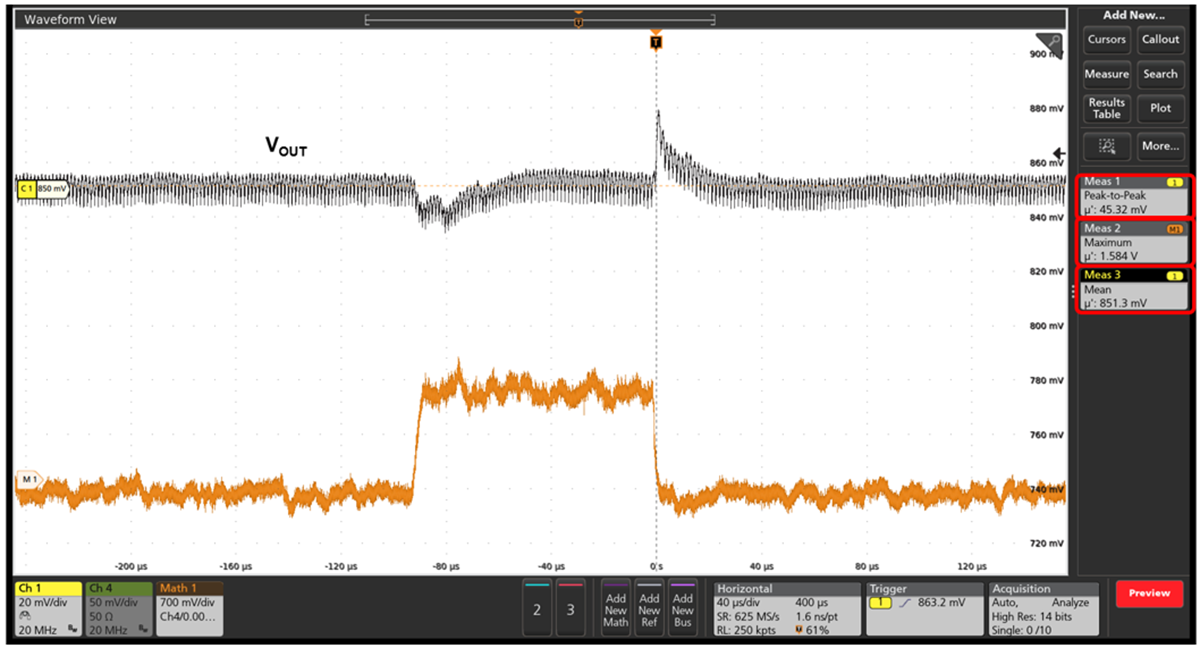

我们对 3A 双输出电源模块 MPM54322 进行负载瞬变测试,来说明满足电压纹波要求所具备的复杂性。为了更好地模拟 FPGA 的行为,我们利用负载冲击器生成瞬态;该冲击器以高达 130A/µs的斜率生成负载阶跃。

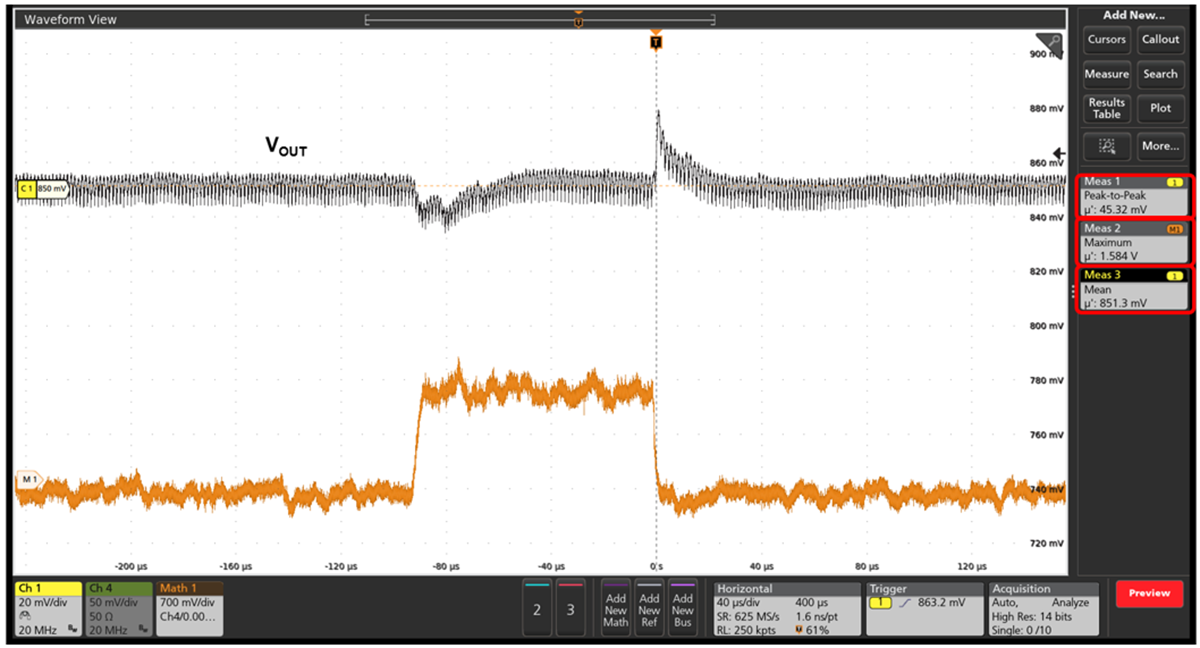

该测试采用 12V 输入电压(VIN)和 0.85V 输出电压(VOUT),以模拟现代 FPGA 设计中最常见的核心电源轨(见图 1)。在负载瞬变测试中,负载从 0A 升至 1.5A,并由电源模块的其中一个3A 输出供电。

图1: 由冲击负载生成的0A 至1.5A负载瞬变

测试表明,该器件在 130A/µs 转换期间的瞬态响应出色,电压峰值为 ±22.5mV。此外,凭借MPS 的自适应恒定导通时间 (COT) 控制,输出电压纹波也在 FPGA 核心轨的容差要求范围内。采用COT 控制,电源可以比传统峰值电流模式控制更快地向负载提供所需的能量。因此无需高输出电容,即可在功率瞬变期间保持稳定的电压。

启动和关断排序

在FPGA应用中,多个电源轨连接至多个稳压器。在电路板启动期间,必须保持启动电源轨的设定顺序,以优化系统效率并最大限度地降低启动电流峰值。但是,由于电路板空间非常有限,用定序器是不现实的。MPS多路输出电源模块(例如 MPM54322)采用 MPS 特有的 FLEX-timer序列控制,无需定序器即可精确控制所有 VR 的启动和关断序列。

确保正确启动

软启动控制

软启动 (SS) 是 FPGA 电源轨的一项关键需求,它可以确保器件可靠地启动并防止对器件造成可能的损坏。该功能通过电压稳压器控制启动期间 VOUT 的上升时间来实现。对于电源轨上有较大容性负载的FPGA来说,软启动尤其重要。如果没有软启动,启动期间的浪涌电流可能会非常高,这有可能导致输入电源电压下降,并损坏 FPGA 或其他组件。

大多数 FPGA 供应商都为其设备指定了约 10ms 的软启动时间(tSS)。随 tSS 逐渐增加电压可以限制浪涌电流,并实现平稳的启动序列。不能满足软启动要求将可能导致各种问题,例如不可靠或非单调启动,以及损坏FPGA 的潜在风险。

为确保可靠的运行,选择符合 FPGA 供应商软启动要求的稳压器非常重要。MPM54322 等稳压器提供可调节 tSS,可根据 FPGA 和电源设计的特殊要求对其进行微调。

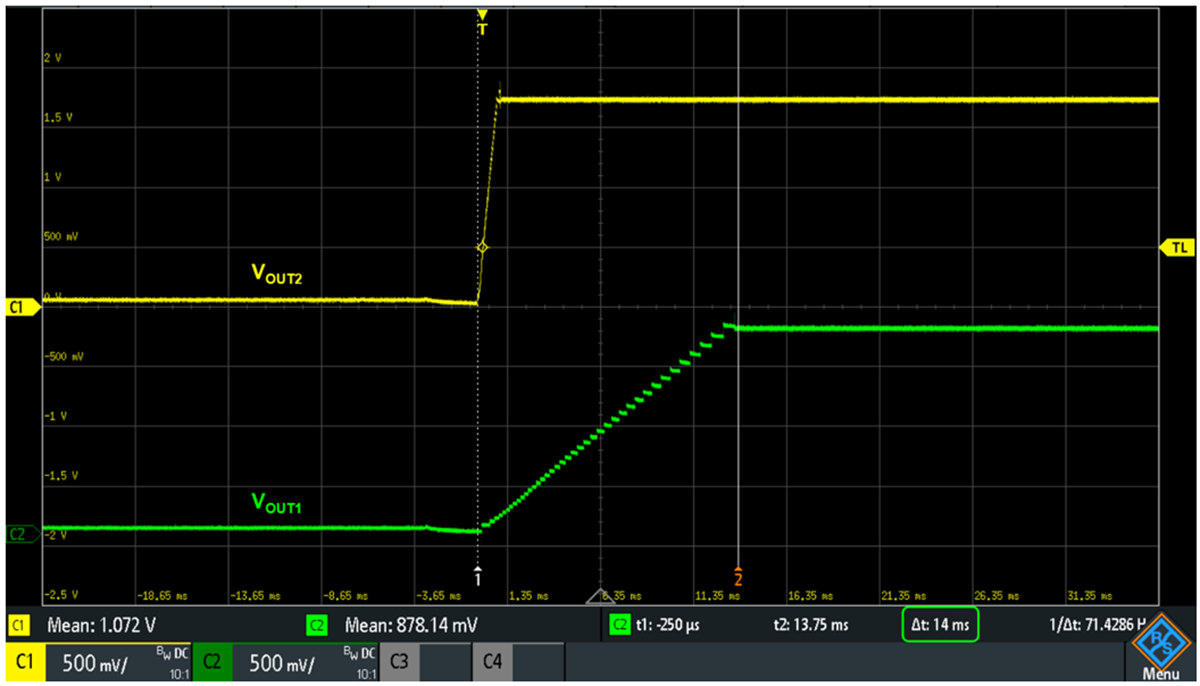

MPM54322 在启动序列中的 tSS 最短为1ms,最长可达14ms(见图 2)。

图 2:两个独立电源轨的启动序列

MPS 特有 FLEX-Timer 序列控制

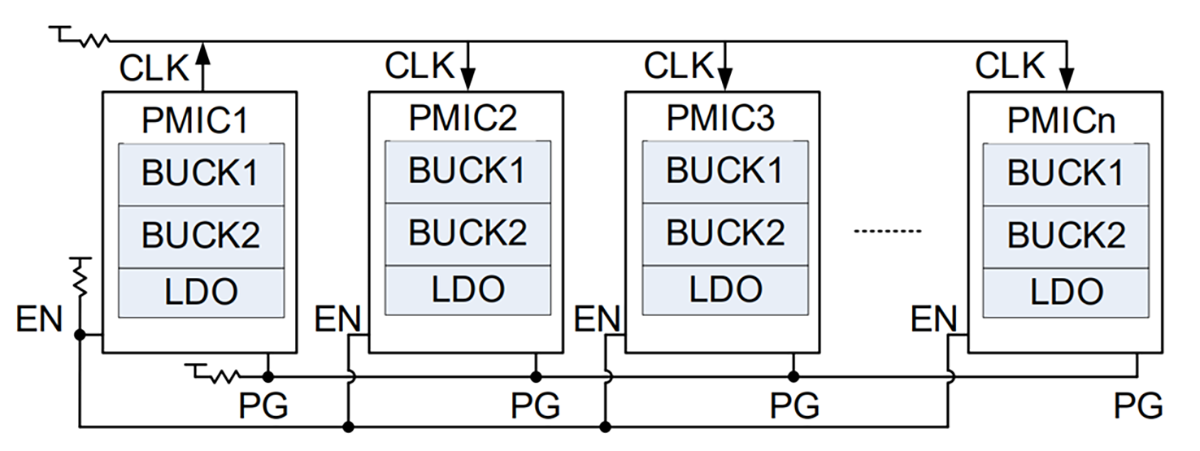

MPM54322 采用 FLEX-timer序列控制技术来实现更好地控制不同电源轨的启动顺序。该控制方案采用主从结构,其中所有电源管理 IC (PMIC) 的控制信号都连接在一起以实现序列协调(见图 3)。

图3: FLEX-Timer序列控制

其中一个 PMIC 被配置为主 PMIC 以生成时钟信号,而其他 PMIC 则配置为从 PMIC 以接收时钟信号。所有电源轨的启动和关断序列都由时钟信号来同步。

当控制信号被置位时,启动序列开始:主 PMIC 生成时钟输出,而从 PMIC 开始计数时钟信号。对每个电源轨来说,当计数的时钟信号周期达到预定义的延迟时,电源轨即导通。

一旦主 PMIC 时钟周期达到预设值,且状态信号指示所有启用的电源轨都已完成软启动过程,则主 PMIC 停止时钟输出,启动序列完成。

在关断期间,如果没有控制信号,主PMIC 即开始生成时钟输出,从 PMIC 开始计数时钟信号。对每个电源轨来说,当计数的时钟信号周期达到预定义的延迟时,电源轨即关断。一旦主 PMIC 时钟周期达到预设值,主PMIC 即停止时钟输出,关断序列完成。

这种序列控制方案在不同 PMIC 管理的多个电源轨上实现了同步且协调的启动和关断过程,无需引入额外的定序器模块。

通过主动放电确保安全关断

VOUT 尖峰可能通过电源轨严重损坏 FPGA。当负载突然被移除时,存储在输出电容 (COUT) 内的能量会在放电时引起高压尖峰。MPM54322 通过输出主动放电来避免这种危害。

主动放电的目的是当负载突然移除或电源关闭时对 PMIC 的 COUT 进行快速放电。FPGA 电源模块会采用大型去耦电容来实现稳定和最佳的电压调节,主动放电可以对这些电容快速放电,从而预防电压尖峰的产生,同时保持正确的关断序列和时序。

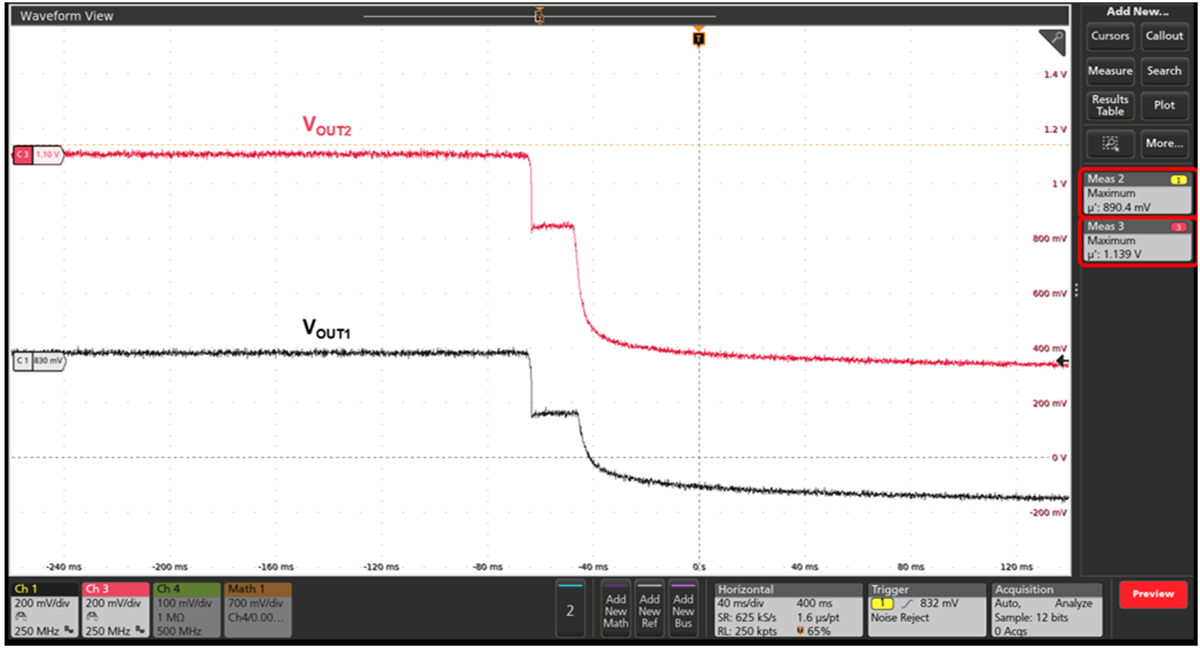

当器件被禁用且内部数模转换器 (DAC) 的输出下降时,将执行主动放电。VOUT 会随着参考电压平稳下降。当 DAC 输出达到 850mV 和 650mV 时,它会保持在这些电压水平,软关断完成。随后,输出通过反馈电阻逐步放电。

图 4 显示了 MPM54322 的关断序列。

图4: MPM54322的关断序列

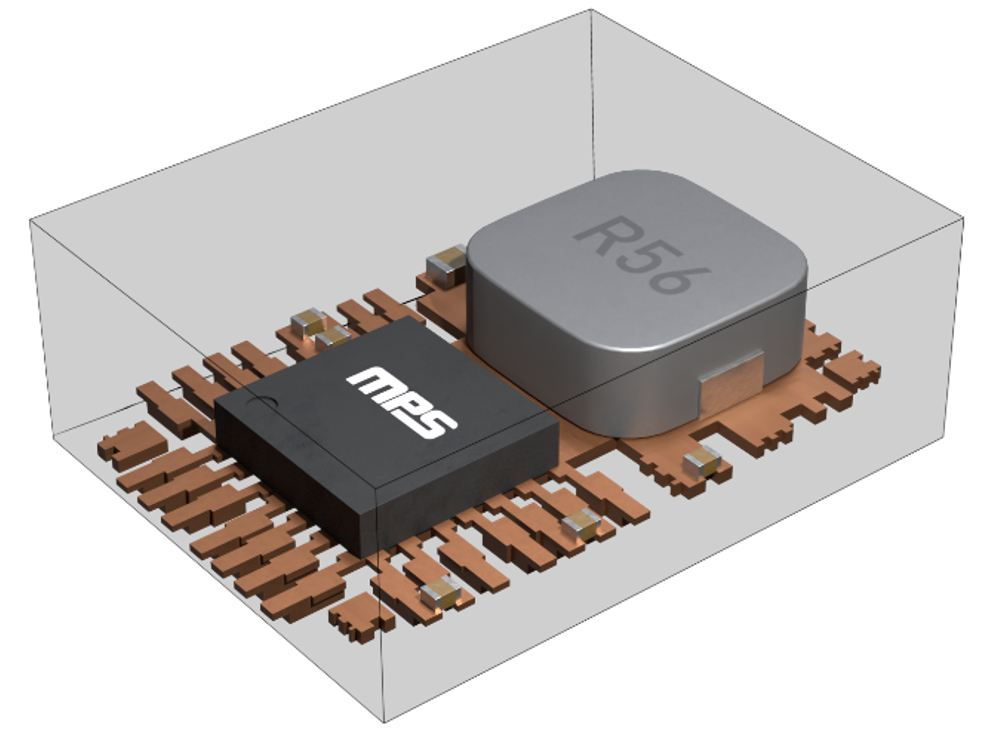

MPM54322简介

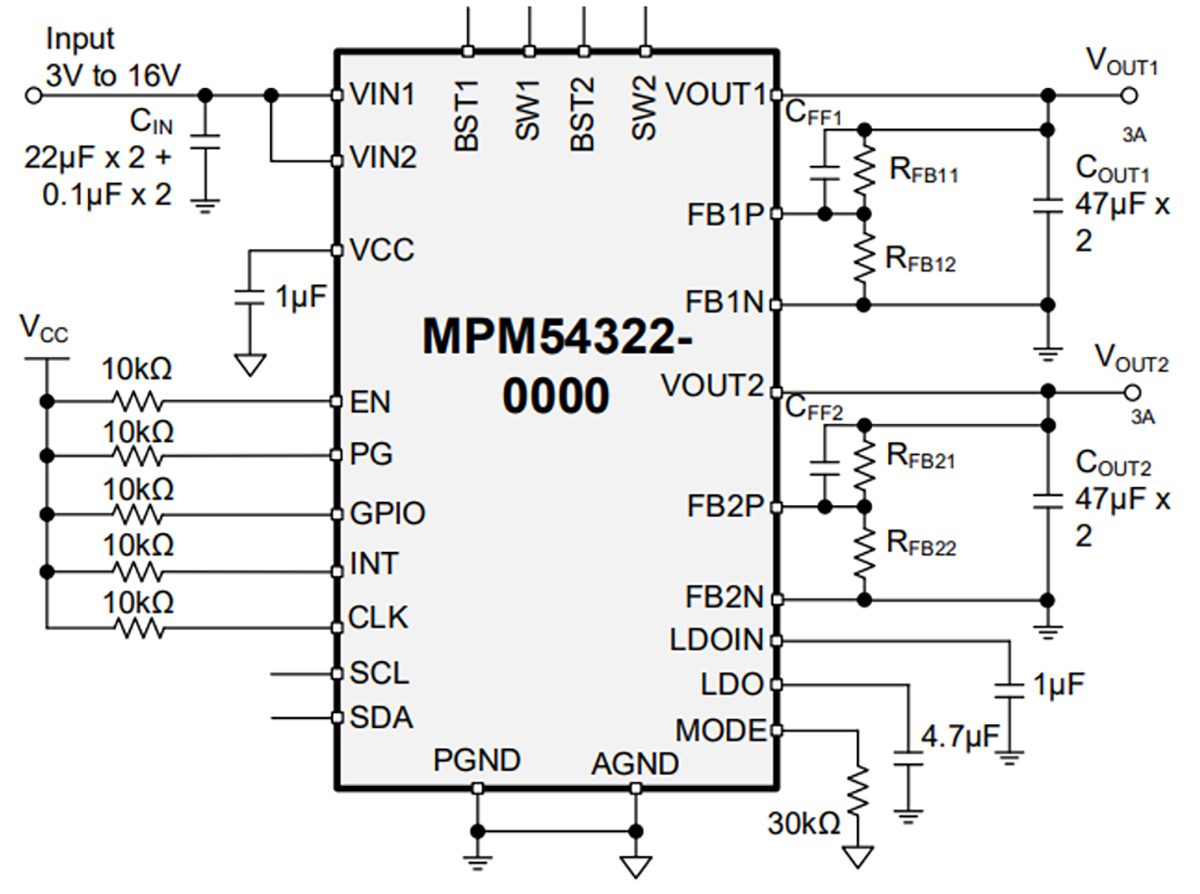

MPS 提供多款灵活且可扩展的多路输出电源模块。其中,MPM54322 是一款 3A 双输出电源模块。它将两个高效率降压 DC/DC 变换器 IC、一个低压差 (LDO) 稳压器和一些无源元件(包括两个用于 DC/DC 变换器的电感)集成到了一个模塑封装中。它的两个输出可单独用来为FPGA的两个独立电源轨供电,也可以并联以提供高达 6A 的电流。

图 5 显示了 MPM54322 的典型应用电路。

图 5:MPM54322 的典型应用电路

如上所述,FPGA 系统中包含了许多与 FPGA 无关的独立系统的电源轨。同一个多输出电源模块也可用于启动其他子系统。鉴于电压和电流的不同,以数字后缀来区分不同的部件可能会导致生产和设置过程中出现混淆,从而对 FPGA 造成可能的损坏。为了解决这个问题,MPM54322 提供了可多达 10 页的多次可编程 (MTP) 页面(具体由连接到 MODE 引脚的电阻决定),允许用户在不同电压的预设可调配置之间进行切换。

结语

随着 FPGA 电源需求的不断提高,要设计出先进FPGA应用所要求的紧凑型电源,先进的多输出电压稳压器(VR)必不可少。

MPM54322等先进电源模块可以实现快速瞬态响应、精确的电压调节,并具有软启动功能和MPS 特有的FLEX-timer序列控制,可确保系统安全的启动和关断。此外,随着系统复杂性越来越高,MPM54322 允许设计人员通过同一设备在 10 个 MTP 页面中轻松选择不同的输出配置,而无需重新配置或使用不同的产品编号。

如需了解更多信息,请浏览 MPS 全面的电源模块产品组合。

_______________________

您感兴趣吗?点击订阅,我们将每月为您发送最具价值的资讯!

技术论坛

Latest activity 2 years ago

Latest activity 2 years ago

2 回复

2 回复

Latest activity 2 years ago

Latest activity 2 years ago

2 回复

2 回复

Latest activity 2 years ago

Latest activity 2 years ago

6 回复

6 回复

直接登录

创建新帐号