Application Requirements

Based on the needs of the application, the choice of the type of ADC and its design is made.

Typical Application Requirements

Typical requirements for an application can include:

Data Rate Requirements: The data rates needed by the application must be supported by the ADC. High data rates are necessary for high-speed applications like digital communications.

Accuracy and precision: ADCs with high resolution are necessary for some applications because they need great accuracy. For instance, high-resolution ADCs are important for medical imaging to record precise data.

Power Consumption: The power limitations of the application should match the power requirements of the ADC. For instance, low-power ADCs are needed for battery-powered applications.

Dynamic Range: In situations where the input signals' amplitudes might fluctuate greatly, a wide range between the lowest and greatest signal levels that the ADC can convert is crucial.

Latency: ADCs with low latency are necessary for some applications, such closed-loop control systems, in order to react promptly to changes in input signals.

Environmental Conditions: Depending on the application, the ADC may need to function in environments with certain requirements, such as vibrations or temperature extremes.

Integration with Existing Systems: The ADC's compatibility with current technological stacks or systems may also be a deciding factor.

Digital Communications Application Requirements

For instance, the following specifications would be necessary if the application was for digital communication:

High Data Rates: Digital communications require very high data rates, especially with the arrival of 5G and beyond. As a result, the ADC should enable large bandwidths and throughput while facilitating the quick conversion of analog signals to the digital realm.

Dynamic Range and Sensitivity: Signals with different amplitudes are frequently dealt with by communication systems. It will be necessary to use an ADC with a good dynamic range to effectively manage these changes.

Integration with Digital Signal Processors (DSPs): ADCs and DSPs frequently collaborate in communication systems to condition and modulate signals. As a result, effective real-time processing ADC integration with DSPs should be achievable.

Scalability and Future-proofing: It is crucial to build a High-Speed ADC that can fulfill scalability requirements and be somewhat future-proof given the constant demand for increased data rates in communication systems.

Market Demand and Impact: Digital communication has a huge market and a significant influence on many businesses as well as daily life. Making a contribution to this sector with a successful ADC design can have significant effects on the industry as a whole.

ADC Selection

Depending on the particular system requirements, many ADC types can be employed in digital communication applications. The choice of ADC depends on elements including speed, resolution, power consumption, and cost, each of which has merits and limitations.

Potential ADCs for Digital Communications

ADCs that are often utilized in applications for digital communication include the following:

Successive Approximation Register (SAR) ADC: Due to fast average speed, excellent resolution, and low power consumption, SAR ADCs are often utilized in a variety of applications. Applications requiring moderate to high precision, such data collecting systems, sensors, and communication interfaces, are ideally suited for them.

Delta-Sigma ADC: High resolution and low noise performance are hallmarks of Delta-sigma ADCs. In audio and communication applications where accuracy and signal integrity are essential, they are frequently employed.

Pipeline ADC: High-speed applications are the focus of pipeline ADC design. They have numerous phases, which enable them to retain a respectable resolution while achieving high conversion rates. In wired and wireless high-speed communication systems, pipeline ADCs are often employed.

Flash ADC: Flash ADCs are among the fastest ADCs currently on the market, however their speed is constrained by their high cost and power consumption. They are appropriate for uses that call for highly fast conversions, including high-frequency communication systems.

Consider the particular needs of the system, such as the needed data rate, accuracy, resolution, and available power budget, when choosing an ADC for a digital communication application. The ideal option will rely on the particular requirements of your application because each form of ADC has trade-offs of its own.

Selecting a Pipeline ADC for Digital Communication Applications

Due to its unique benefits that fit well with the needs of such systems, a pipeline ADC might be a good option for some digital communication applications. Here are some factors that might influence the decision to use a pipeline ADC in a digital communication application:

High-Speed Conversion: The high-speed capabilities of pipeline ADCs are well recognized. They employ a pipeline structure with numerous steps, which enables them to achieve high conversion rates. The high-speed conversion of a pipeline ADC might be useful in digital communication systems where real-time data processing and quick signal capture are necessary. Few mega samples per second (Msps) to 100Msps+ are typical sampling rates for pipeline ADCs.

Moderate to High Resolution: Pipeline ADCs are capable of providing low to high resolutions. A pipeline ADC can obtain greater overall resolution than a single-stage ADC by cascading many resolution-each stages. The proper representation and reconstruction of analog signals in digital communication applications is critical. Between eight bits at the higher sampling rates and 16 bits at the lower sampling rates, Pipeline ADCs may handle a variety of resolutions.

Compatibility with High-Speed Interfaces: Pipeline ADCs are particularly suited for interacting with high-speed serial interfaces (such as USB 3.0) and optical communication systems, as well as high-speed digital communication protocols like Gigabit Ethernet. They can keep up with the high data rates of these communication interfaces because of their quick conversion rates.

Lower Power Consumption than Flash ADCs: Pipeline ADCs are better ideal for power-constrained digital communication devices, especially in battery-operated applications, even though they are often quicker than Successive Approximation Register (SAR) ADCs.

Versatility: Pipeline ADCs are appropriate for a variety of digital communication interfaces and protocols with variable signal amplitudes because they can handle a broad range of input signal levels.

Reduced System Complexity: Comparing pipeline ADCs to other high-speed ADCs like Flash ADCs, simpler topologies are frequently present. This can make the design of the entire system simpler, make clocking and synchronization less difficult, and make it easier to integrate the ADC into the communication system.

Precise Timing and Synchronization: For applications requiring precise timing and synchronization between the ADC and other parts of the digital communication system, pipeline ADCs with well-defined pipeline delays can be useful.

Software-defined radios (SDRs), digital receivers, wireless communication systems, high-speed data transfer, and communication test equipment are just a few examples of digital communication applications that frequently employ pipeline ADCs. To decide if a pipeline ADC is the best option for a given use case, it is crucial to take into account the unique needs of the digital communication application and the trade-offs involved, such as power consumption and cost. Additionally, the overall system needs and factors, such as the needed resolution, speed, accuracy, and power budget, should be taken into account when selecting an ADC.

Introduction to Pipeline ADC

Recap of Pipeline ADC Architecture

An ADC (Analog-to-Digital Converter) pipeline is a high-speed ADC that divides the analog-to-digital conversion process into many stages or pipeline segments in order to achieve rapid conversion rates. Up until the final digital output is generated, each step processes a portion of the input signal, and the outcomes are then passed along to the following stages. The parallel processing of the analog input made possible by the pipeline design enables for high-speed conversion rates while keeping adequate precision.

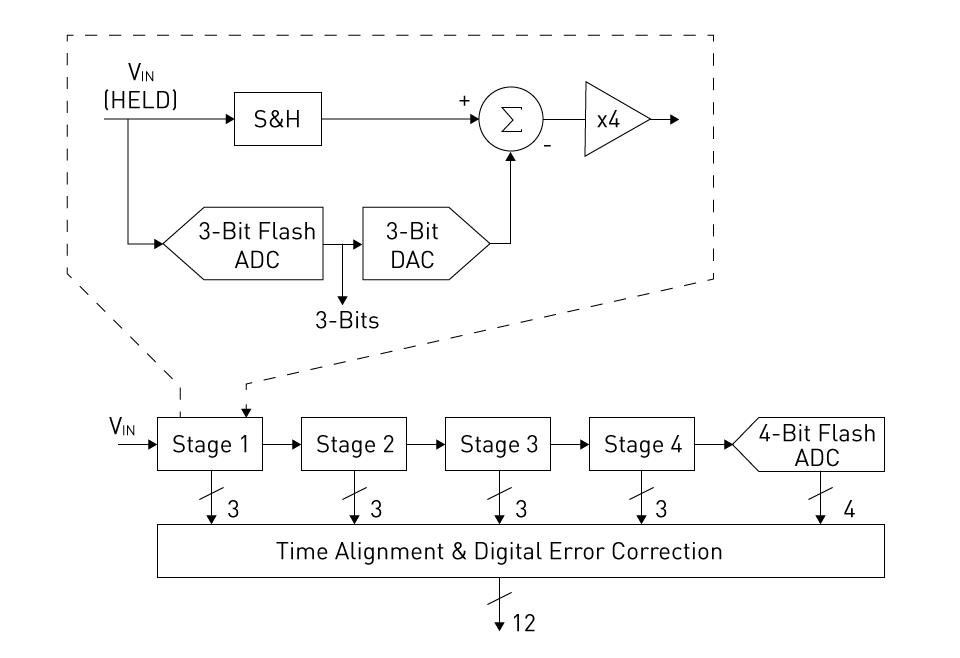

Figure 1: 12-bit pipelined ADC

The pipeline ADC's foundational ideas are as follows:

Stages: Multiple stages, typically four or more, are stacked in sequence to make up an ADC pipeline. The analog input signal is partially converted to digital form at each stage.

Pipelining: A pipeline structure is created by processing each step's output before passing it to the stage after it. Each step in the pipeline that the analog signal takes helps to improve the digital representation of the input.

Time-Interleaving: Some pipeline ADCs employ the method of time-interleaving to boost conversion rates even more. The effective sampling rate and conversion speed are increased further by employing numerous parallel pipelines that sample the input signal at various intervals.

Multiplexing and Demultiplexing: Usually, the incoming signal is multiplexed into smaller chunks, with each chunk being transmitted to a different stage for parallel processing. The final digital output of the ADC is created by demultiplexing and combining the digital outputs from each step.

Calibration and Error Correction: Mismatches between stages may cause extra mistakes to be introduced into pipeline ADCs. Calibration methods and error-correction algorithms are frequently used to reduce these faults and increase accuracy and linearity.

Digital Processing: To create the final output, the digital outputs from each stage must be merged and processed in the digital domain. Timing, synchronization, and data alignment are handled by digital logic to assure proper representation of the analog input signal.

Pipeline ADCs are frequently employed in systems for digital signal processing, wireless communication, optical communication, and high-frequency data collection when high-speed conversion is essential. They are suitable for high-throughput applications needing quick and accurate analog-to-digital conversion and offer a good balance between speed and resolution.

In contrast to other ADC types like Successive Approximation Register (SAR) ADCs or Sigma-Delta ADCs, they could be more sophisticated and use more power. The selection of a pipeline ADC, like any other ADC option, should be based on the particular application needs and the intended trade-offs between speed, resolution, power consumption, and complexity.

Significance of High-Speed Data Conversion

Data processing in real-time or close to real-time is necessary for many applications, including telecommunications, medical imaging, radar systems, and high-performance computers. For these applications, high-speed data conversion is essential because it enables prompt digitization of analog signals, which may subsequently be effectively processed, stored, or sent.

In digital communications, for example, the support for larger bandwidths and data rates is enabled by the capacity to rapidly transform analog signals to digital form. For new communication standards, which demand support for extremely high data rates, this is especially crucial.

High-speed data conversion is essential in medical imaging to capture quickly varying biological signals in high resolution. This is especially important in applications like ultrasound or MRI, where rapid data processing is necessary to provide high-quality pictures.

Pipeline ADCs combine the high data rate capability with the efficiency and precision of the SAR design. Because of this, they are indispensable in situations where both accuracy and speed are necessary.

Design Process

Specifications

To make sure that the pipeline ADC satisfies the needs of the desired application, it is essential to describe the important parameters precisely while developing the device. The essential requirements to define include:

Resolution: The quantity of discrete output levels that an ADC can represent depends on its resolution. Typically, it is defined in bits (12-bit or 16-bit, for example). The ADC can deliver more precise readings with higher resolution.

Sampling Rate: The sampling rate determines how quickly the analog input is sampled by the ADC before being transformed into a digital output. Samples per second (SPS) or mega-samples per second (MSPS) are typically used to specify it. The input signal's highest frequency components should be accurately captured by the sampling rate.

Input Range: The analog input voltage range that the ADC may tolerate without saturation or clipping is defined by the input range. The input range must allow for the predicted input signal amplitudes without overloading or introducing distortion.

Signal-to-Noise Ratio (SNR): SNR is a metric for how well an ADC can tell a signal from noise. It displays the output's ratio of signal power to noise power. Better noise performance and, as a result, more precise measurements are indicated by a higher SNR.

Total Harmonic Distortion (THD): THD, which is calculated as the ratio of the total of the harmonic components to the fundamental signal, quantifies the distortion caused by the ADC. Better linearity and less distortion are correlated with lower THD.

Integral Non-Linearity (INL) and Differential Non-Linearity (DNL): The ADC's linearity is measured by INL and DNL. INL depicts the difference between the real and ideal transfer functions, whereas DNL measures the step size discrepancy between neighboring output codes. For correct signal representation, INL and DNL should both be reduced.

Power Consumption: The ADC's power consumption is critical for battery-powered applications to maximize battery life. To make sure the ADC's power needs are in line with the overall system limits, specify the maximum permitted power usage.

Latency: The time elapsed between the input signal and the matching digital output is referred to as latency. Low latency is essential in some digital communication applications to prevent delays and provide real-time data processing.

Dynamic Range: The dynamic range of an ADC is the range between the largest and smallest input signals that it can faithfully represent (those bigger than the noise floor). To accurately capture both weak and powerful input signals, a large dynamic range is necessary.

Operating Temperature Range: Specify the operating temperature range where the ADC is predicted to operate safely. For use in severe or extreme situations, this is especially crucial.

EMI/EMC Considerations: To guarantee that the operation of the ADC does not contribute undesired noise or interference into the system or surrounding components, take into account standards relating to electromagnetic interference (EMI) and electromagnetic compatibility (EMC).

The design team may make sure that the pipeline ADC satisfies the particular demands and performance criteria of the digital communication application by precisely specifying these fundamental parameters. To ensure the best performance and accuracy in the finished product, these standards will serve as a guide during the design phase and the component selection process.

Choice of Components

The selection of the parts that will go into the pipeline ADC is the next stage. Included in this is the option of:

Sample-and-Hold (S/H) Circuit: During the conversion process, the analog input voltage must be captured and held by the S/H circuit. To achieve precise and reliable voltage sampling, it is essential to use an appropriate S/H circuit.

Analog Input Buffer: To protect the ADC from the source impedance of the input signal and offer high input impedance, an analog input buffer could be necessary. The buffer lessens the impacts of loading and aids in maintaining signal integrity.

Voltage References: For accurate analog-to-digital conversion to occur, precise and steady voltage references must be used. Select voltage references that offer low drift and noise performance and match the necessary voltage range for the ADC.

Clock Source: To manage the conversion process, the ADC requires a steady and reliable clock source. The ADC's speed, timing, and jitter performance are all affected by the clock source used. To ensure dependable and exact sampling, consider utilizing a high-quality clock source.

Op-Amps and Amplifiers: For signal conditioning and gain modifications, opto-amps and other amplifiers may be required, especially if the input signal requires amplification or attenuation to match the ADC's input range.

Digital Processing Components: To manage data flow and timing throughout the many stages, the pipeline ADC requires digital processing components such as flip-flops, logic gates, and digital multiplexers.

Comparator: A comparator is used in each stage of the pipeline ADC to compare the analog voltage to a reference voltage. The performance of the comparator influences the ADC's speed and accuracy.

Control Logic and Timing Circuitry: The ADC requires control logic to regulate pipeline stages, timing signals, and stage synchronization. Proper timing circuitry guarantees that the ADC operates precisely.

Power Supply Components: Choose suitable power supply components to give clean and reliable power to the ADC while minimizing noise and interference.

Support Components: Consider the extra support components necessary for biasing, filtering, and impedance matching, such as resistors, capacitors, and inductors.

Layout and Schematic Design

Schematic Design: Make a complete schematic diagram of all the essential components, such as the sample-and-hold circuit, analog input buffer, voltage references, comparators, digital processing elements, and clock circuits.

Component Selection and Placement: Select high-quality components that fulfill the specs and performance requirements of the pipeline ADC. Optimize component layout to decrease signal routes, limit parasitic effects, and maximize board space.

Layout Design: Make use of a well-structured and ordered layout design that takes signal integrity, grounding, and power distribution into account. To decrease crosstalk and interference, route essential analog signals away from noisy digital traces.

Verification: Check that the layout follows the production limitations and avoids any fabrication difficulties. To confirm that all connections are proper and complete, compare the layout to the original schematic. If feasible, simulate the layout to evaluate its performance and signal integrity under various operating scenarios.

Design Verification and Testing

A set of processes are involved in verifying the design of a pipeline ADC in a digital communication application to guarantee that the ADC fits the required specifications and functions properly. The following are the important stages for validating the ADC design:

Simulation and Modeling: To validate the ADC's functionality and performance, run extensive simulations with SPICE or other relevant simulation tools.

Functional Testing: Fabricate a pipeline ADC prototype and perform functional testing to ensure its functionality under real-world settings. Under various input settings, evaluate the ADC's linearity, precision, and noise performance.

Timing and Synchronization Testing: Check the timing and synchronization of the pipeline ADC's various stages. Ascertain that the pipeline delay and timing characteristics fulfill the specifications.

Power and Efficiency Analysis: Measure the ADC's power consumption under various operating situations to ensure it is consistent with the digital communication device's power budget.

Linearity and Error Correction: Calibration procedures and error-correction algorithms, if applicable, should be used to assess the ADC's linearity and accuracy.

Noise and Distortion Analysis: Under varied input circumstances and sampling rates, characterize the ADC's noise performance, including signal-to-noise ratio (SNR) and total harmonic distortion (THD).

Integration with Communication System: Integrate the ADC into the digital communication system and assess its compatibility and performance in comparison to other components.

Environmental Testing: To assure the ADC's stability and dependability in multiple working situations, conduct testing under varying environmental variables (e.g., temperature, humidity).

Engineers may reliably verify the pipeline ADC's performance and appropriateness for the digital communication application by following these verification processes. Address any design flaws or improvements discovered during testing, and iterate the design as needed to attain peak performance and accuracy.

Implementation and Integration

Embedding Pipeline ADC in System Design

Here are the four most important factors to consider while embedding a pipeline ADC in a target system:

Power Supply and Decoupling: Give the ADC a clean and reliable power source. Install decoupling capacitors near the ADC's power pins.

Signal Integrity and Layout: Design the arrangement carefully to reduce signal interference and crosstalk. Avoid routing sensitive analog traces near noisy digital signals.

Clock Source and Timing: Assure that the ADC has a steady and accurate clock source. Distribute the clock signal correctly to all stages of the ADC.

Digital Interface and Data Processing: Create a digital interface that is compatible with the communication protocols and data processing units of the target system. Check that the ADC's output data type and timing are compatible with the system requirements.

Engineers may achieve optimal performance and accuracy by carefully examining these parameters and smoothly integrating the pipeline ADC into the target system, making the ADC an effective and dependable element of the entire system architecture.

System-Level Verification

After integrating the Pipeline ADC into the system, it is critical to ensure that it works as intended in the context of the complete system:

Performance Testing: Under various operating situations, evaluate the ADC's resolution, linearity, accuracy, and noise performance. Confirm that the output of the ADC appropriately represents the analog input signal within the specified dynamic range.

Speed and Timing Verification: Verify that the ADC's conversion speed satisfies the specified sample rate and throughput. Ensure that the ADC and other system components are precisely timed.

Interface Compatibility: Check that the ADC's digital output interface is compatible with the data processing units and communication protocols of the system. Check that the output data format and timing of the ADC are compatible with the requirements of downstream digital components.

Power Consumption and Efficiency: Measure the ADC's power usage in various conditions to ensure it is consistent with the system's power budget. To improve its integration into the target system, evaluate the ADC's efficiency in terms of power use and performance.

Optimization for Performance

Optimizing a pipeline ADC for a digital communication system entails increasing its performance and efficiency to match the application's unique needs. Here are the four stages to accomplishing this optimization:

Performance Characterization and Calibration: To understand the pipeline ADC's strengths and limits, do a detailed performance characterization. Calibration procedures should be used to adjust for any non-linearity or offset problems in the ADC's output, hence enhancing its accuracy and precision.

Noise Reduction and Signal Conditioning: Implement noise reduction measures to reduce the ADC's performance effect from noise. Proper grounding, shielding, and filtering procedures may be used. Consider adding signal conditioning hardware, such as amplifiers or filters, to increase the dynamic range and overall sensitivity to the input signal of the ADC.

Timing and Synchronization Optimization: Optimize the pipeline ADC's timing and synchronization to achieve exact alignment with other components in the digital communication system. Use clock distribution strategies to reduce clock jitter and increase the ADC's overall timing accuracy.

Power Management and Sleep Modes: Use power management strategies to optimize ADC power usage, particularly in battery-powered systems. Reduce power consumption during idle periods or when the ADC is not actively converting by using sleep modes or power-down capabilities.

Results and Analysis

Performance Metrics

A pipeline ADC's performance may be evaluated using a variety of parameters. These measurements aid in quantifying the ADC's strengths and limits, offering vital information into its applicability for a certain application. Here are some critical performance indicators:

Resolution: The number of bits utilized to represent the ADC's digital output, indicating its ability to record minor changes in input voltage properly.

Signal-to-Noise Ratio (SNR): The signal-to-noise power ratio in the ADC's output, demonstrating its capacity to discern between signal and noise.

Total Harmonic Distortion (THD): Harmonic distortion caused by the ADC, affecting its linearity and accuracy.

Effective Number of Bits (ENOB): The number of bits of effective resolution attained under real-world settings, taking noise, distortion, and nonlinearity into consideration.

Power Consumption: The amount of power utilized by the ADC, which is particularly important in battery-powered systems in order to maximize efficiency and battery life.

Recommendations for Improvements

The following critical metrics may be evaluated to improve the performance and design of a pipeline ADC:

Resolution: Increasing the ADC's resolution enhances its capacity to represent subtle fluctuations in the analog input, resulting in increased accuracy and precision.

Signal-to-Noise Ratio (SNR): SNR is improved by reducing noise sources in the ADC's analog front-end and digital processing stages, allowing the ADC to collect weaker signals more accurately.

Dynamic Range (DR): By increasing the ADC's dynamic range, it can tolerate a wider range of input signal amplitudes without saturation or clipping, resulting in greater performance over a wider range of signal levels.

Linearity (DNL and INL): These enhancements may include better circuit design, component selection, calibration procedures, and layout considerations.

By focusing on these key metrics, design optimizations can be made to enhance the pipeline ADC's performance, making it more suitable for the target application. These improvements may involve refined circuit design, component selection, calibration techniques, and layout considerations.

直接登录

创建新帐号