Introduction to High-Speed ADCs

Defining High-Speed ADCs

High-Speed ADCs, also known as High-Speed Analog-to-Digital Converters, are specialized ADCs crafted to function at extremely fast sampling rates. Although the idea of "high-speed" can be relative and may change over time, as of now, it generally pertains to ADCs with sampling rates between several hundred megasamples per second (Msps) and several gigasamples per second (Gsps).

High-Speed ADCs play a vital role in situations where there is a need to convert wide bandwidth signals into digital form with accurate detail. These ADCs use different structures, such as pipeline, flash, or time-interleaved ADCs to accomplish the rapid conversion process.

Importance in Broadband Communications and Software Defined Radios

In the realm of communication, 'broadband' as a term signifies the wide range of signal bandwidth used for transmitting information. With the ongoing increase in data rates within communication systems, the signals representing this data now occupy a broader bandwidth. High-Speed ADCs play a crucial role in these systems by enabling the conversion of these expansive signals into digital form, allowing for diverse digital processing methods.

A pivotal domain for High-Speed ADC applications lies in Software Defined Radios (SDRs). Unlike traditional radios that rely on hardware for specific tasks like modulation or filtering, SDRs utilize software for these radio functions, this grants SDRs the ability to modify their behavior without altering the hardware, resulting in exceptional flexibility and adaptability to new communication standards.

In the realm of SDRs, the capability to handle signals spanning a broad array of frequencies holds great importance. High-Speed ADCs facilitate this by converting wide bandwidth signals into digital form, enabling software to manipulate them. This is particularly crucial given the swift evolution of communication technologies, where the capacity to seamlessly adopt new standards without hardware adjustments proves highly advantageous.

Furthermore, SDRs frequently find applications in systems accommodating multiple standards and frequency bands. Here, the wide bandwidth processing made possible by High-Speed ADCs becomes indispensable, enabling a single SDR platform to communicate across various standards and frequency ranges.

Key Parameters and Challenges

High-Speed ADCs, essential for Software Defined Radios (SDRs) and broadband communications have their special requirements and difficulties. The key to optimizing system performance is to understand these factors.

Sampling Rate

The sampling rate is one of the key factors for High-Speed ADCs. It specifies how many samples are collected every second. It's usually quantified in Msps (Mega samples per second) or Gsps (Giga samples per second). The Nyquist-Shannon sampling theorem establishes that the sampling rate needs to be at least two times the bandwidth of the bandpass signal or twice the highest frequency part of the baseband input signal to faithfully rebuild the signal. In scenarios with high-speed requirements, like broadband communication, the sampling rate must be notably elevated to accommodate the extensive bandwidths at play.

Resolution

Resolution is the number of bits required to digitally represent each sample. The typical challenge for high-speed ADCs is striking an acceptable balance between resolution and sampling rate. A higher resolution enables a more precise representation of the input signal, but because the conversion process is more complex, it tends to lower the maximum feasible sampling rate. To maintain signal quality across several radio standards, a reasonably high resolution is required in applications such as SDRs.

Spurious-Free Dynamic Range (SFDR)

SFDR stands as a crucial yardstick for gauging High-Speed ADC performance. It gauges an ADC's aptitude to differentiate a desired signal amid noise and unwanted signals.

Figure 1: Spurious-free Dynamic Range

SFDR is determined by comparing the root mean square (RMS) amplitude of the fundamental signal with the RMS value of the next most prominent unintended content in the frequency domain. It's commonly expressed in dBc (decibels concerning the carrier signal amplitude) or dBFS (decibels concerning the ADC's full-scale range). The significance of SFDR arises from the fact that nonlinearities within high-speed ADCs can induce harmonic distortion and spurious frequencies. Elevated SFDR values indicate that undesirable components are markedly lower than the desired signal, which holds great importance in broadband communication systems where maintaining a clear spectrum is pivotal.

Power Consumption

The complexity of the ADC architecture grows along with the sample rates and resolution, leading to increasing power consumption. Power efficiency is crucial in many applications, particularly in portable and battery-operated devices. High-Speed ADCs must be designed to satisfy performance requirements while using the least amount of power possible. This problem can be solved utilizing methods including power scaling, ADC architecture optimization, and the use of contemporary low-power semiconductor processes.

ADCs in Broadband Communications

High-speed ADCs enable the conversion of signals into digital form, which can be processed and sent effectively, playing a crucial part in broadband communications.

Role in Modulation and Demodulation

Broadband communication systems heavily rely on diverse modulation techniques to transmit data across wide bandwidths. Within the digital modulation procedure, the ADC transforms baseband signals into digital format, ready for modulation onto a carrier signal for transmission. Similarly, on the receiving side, the ADC plays a pivotal role in demodulation. It transforms the received signal into digital form, enabling subsequent processing to recover the initial information. Devoid of the ADC, the task of converting and handling the immense data volumes conveyed through broadband communication systems would be nearly insurmountable.

Design Considerations for High Data Rates

When implementing ADCs, several design considerations must be made to manage the high data rates common to broadband communication systems:

Sampling Rate: To faithfully represent the signal, the ADC's sampling rate must be adequately high, usually double the peak frequency of the baseband signal or the bandwidth of the bandpass signal.

Resolution: For swift data rates, the resolution should be chosen thoughtfully to ensure the ADC can manage the intended signal quality without excessively boosting complexity and power usage.

Bandwidth: The ADC's bandwidth must be ample to handle the array of frequencies present in the broadband signal.

Linearity: Effective linearity in the ADC is crucial for minimizing harmonic distortion, which can diminish the quality of the received signal.

Clock Jitter: Clock jitter, a concern for high-speed ADCs, can harm the signal-to-noise ratio (SNR). The clock source should be stable, featuring low-phase noise.

Power Consumption: Crafting for elevated data rates often correlates with increased power consumption. Balancing performance and power efficiency is vital, especially in portable devices.

Case Study: Implementation in a Broadband Modem

Let's delve into a case study involving the integration of a high-speed ADC within a broadband modem. Modern broadband modems are capable of supporting data rates reaching several hundred Mbps or even Gbps. Achieving this demands the presence of a high-speed ADC.

Taking a typical DOCSIS (Data Over Cable Service Interface Specification) 3.1 cable modem as an example, the downstream data gets modulated through Quadrature Amplitude Modulation (QAM). Here, the employed ADC needs to possess a sufficiently high sampling rate for accurate sampling of the incoming signal, which can span the GHz range. Moreover, the ADC's SFDR needs to be substantial to accommodate the signal's broad dynamic range without introducing distortion.

A modern DOCSIS 3.1 modem, for instance, might use an ADC with a sampling rate of several Gsps, a resolution of 12 to 14 bits, and an SFDR of more than 60 dB. This would maintain the integrity and quality of the signal while enabling the modem to handle multi-Gbps traffic speeds. To obtain greater effective sampling rates without considerably increasing power consumption, the ADC may also employ techniques like time-interleaving.

ADCs in Software Defined Radios (SDRs)

The architecture of radio communication networks has been completely redesigned by the revolutionary technology known as Software Defined Radio (SDR). SDRs are made to be very versatile, with software being used in place of typically built hardware elements including mixers, filters, and amplifiers.

Concept of SDR and its Importance

The use of software-based processing for modulation, demodulation, and signal processing is the fundamental idea that supports SDR. This suggests that by just changing the software, the same hardware can be utilized for various communication standards and applications. SDRs are highly adaptable to new communication protocols and standards, thanks to their flexibility, which makes them simple to reconfigure and upgrade. Additionally, SDRs can enable wireless devices with many modes, multiple bands, and/or multiple functions that can be dynamically altered by software.

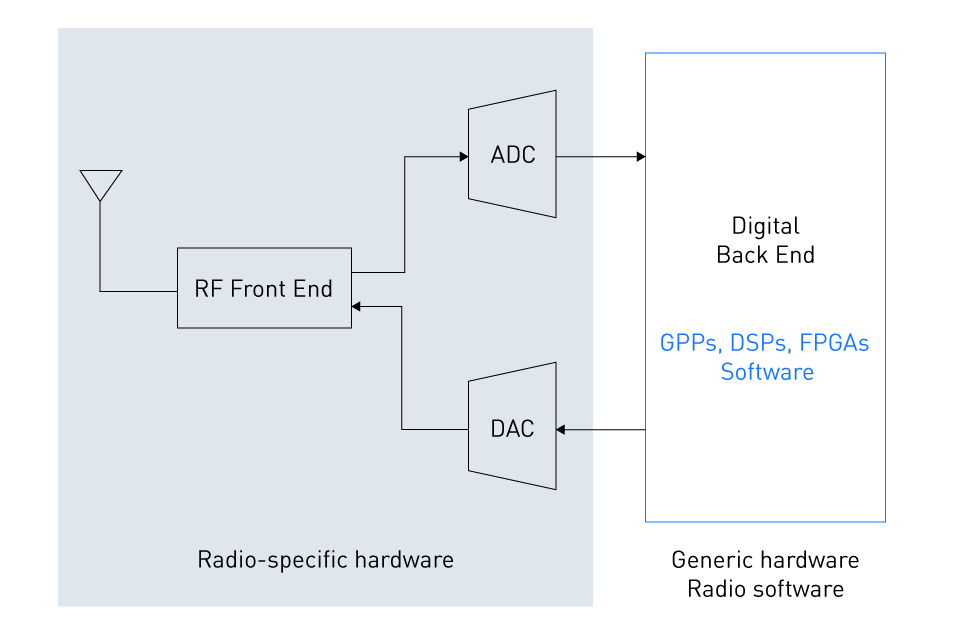

Figure 2: SDR architecture

Role of High-Speed ADCs in SDR

Before being supplied to the ADC in SDRs, the analog signals from the antenna must first pass through a front-end component that may include amplifiers and filters. These analog signals are subsequently converted to digital by the ADC, and all subsequent processing is carried out digitally.

High-Speed ADCs play a pivotal role in guaranteeing the capability of SDRs to accommodate wide signal bandwidths, allowing them to operate effectively across various frequencies and standards. The ADC's sampling rate must meet the Nyquist criterion for the highest frequency the SDR is meant to handle. Moreover, a high-resolution ADC is indispensable to ensure the digital rendition of the signal retains ample accuracy for subsequent digital signal processing.

The inherent flexibility of SDRs often necessitates their operation over an expansive frequency and modulation range. This amplifies the significance of ADCs, as a high-speed, high-resolution ADC empowers the SDR to manage a broad array of signals without an excessive requirement for elaborate analog front-end processing.

Case Study: Design and Implementation of an SDR for Wireless Communication

Consider an SDR that is built for wireless communication and can process both Wi-Fi and cellular signals.

The ADC for this application must be capable of handling the frequency bands used by both cellular networks (varying from 700 MHz to several GHz) and Wi-Fi (2.4 GHz and 5 GHz). An ADC having a sampling rate of at least 10 Gsps (giga-samples per second) could be used in this situation.

Resolution is essential, in addition to great speed. To offer the requisite dynamic range and sensitivity for weak signals, a 14-bit or 16-bit ADC could be chosen.

The selected ADC might be integrated with other digital components as part of a larger FPGA or ASIC. The digital processing performed by the SDR may be handled by an FPGA, enabling real-time algorithm modification.

The purpose of the ADC is to continually convert incoming signals from analog to digital. The FPGA or processor can then carry out programmed functions like filtering, demodulation, and decoding that can be altered in accordance with the communication standards.

A smartphone or a communication node in a heterogeneous network may use this SDR to switch between Wi-Fi and cellular networks on the fly.

直接登录

创建新帐号