Introduction to Power Consumption in ADCs

Power consumption in Analog-to-Digital Converters (ADCs) is now of utmost importance due to the widespread use of electronic devices and the rising demands for portability and energy efficiency. In this section, we'll explain the importance of power consumption and look into the different factors that affect how much power ADCs use.

Relevance of Power Consumption

Battery Life: Extending the battery life is essential for portable electronics like smartphones, wearables, and Internet of Things (IoT) sensors. Because the ADC's power consumption directly affects battery life, it's crucial to keep it to a minimum.

Heat Dissipation: Over time, the electricity used dissipates as heat. Managing the heat produced is essential in systems where ADCs operate at high speeds or in dense designs to prevent thermal throttling or damage.

System Efficiency: The power consumption of the ADC has an impact on the overall efficiency of systems with constrained power budgets such as embedded systems or remote sensors. The ADC must carry out its conversion jobs while staying within the power budget and preserving the necessary performance

Green Computing: With the increased attention being paid to energy use and the effects it has on the environment, cutting back on power usage is also part of a larger effort to adopt more environmentally friendly and sustainable computing methods.

Sources of Power Consumption in ADCs

Switching Activity: The ADC's switching activity is one of the main drivers of energy consumption. A transistor inside the ADC uses energy whenever it changes states. More switching happens with a higher operating frequency for the ADC, which increases power usage

Static Currents: Leakage currents continue to flow through the circuit even when transistors are not switching. Leakage currents have grown to be a significant part of power consumption in modern CMOS technologies as the feature size decreases

Input Drivers and Buffers: Buffers and input drivers are needed to drive the input signal into the ADC, particularly if the input impedance is low. Buffers that drive the ADC inputs can also use a lot of energy.

Reference Voltage Generation: Many ADCs require the generation of a stable reference voltage. It frequently necessitates additional circuitry, which uses power to generate this reference voltage.

Digital Circuitry: The ADC's counters, logic gates, and registers are all digital components that require power. Both switching-related dynamic power and leakage current-related static power are included in this.

Output Drivers: The ADC output drivers use energy, especially in parallel output interfaces where several bits are pushed concurrently. These drivers send the digital output to the next stage in the processing chain.

Standby Modes

Power management is crucial in the context of ADCs for enhancing performance and increasing battery life for portable devices. The use of standby modes is one of the most efficient power management strategies. The essential ideas of standby mode will be explained in this section along with how it assists with power conservation, how to enter and exit this mode, and some typical use scenarios.

Basic Concepts of Standby Mode

An ADC can enter standby mode, a low-power condition when it is not actively carrying out conversions. In this mode, the ADC keeps its configuration and settings while drastically reducing its power consumption by turning off specific internal circuits and functions. To enable the ADC to awaken rapidly when necessary, the core logic is frequently kept powered, but at a significantly reduced power level.

Power Saving in Standby Mode

Power saving in standby mode is achieved by several means:

Clock Gating: By limiting or deactivating the clock signals to the ADC's non-essential components, switching activity is reduced and power is conserved.

Voltage Scaling: By decreasing the supply voltage to some ADC components, it is possible to save a quadratic amount of power.

Disabling Input Buffers and Output Drivers: Both input buffers and output drivers have the potential to consume a lot of power. Power can be saved by either disabling them or putting them in a high-impedance state.

Reducing Leakage Current: In standby mode, some transistors can be set up in a way that reduces leakage current.

Entering and Exiting Standby Mode

The system frequently writes a certain pattern to a control register inside the ADC in order to activate internal logic that switches the ADC into standby mode. As previously mentioned, this typically entails disabling various internal clocks, reducing voltages, and turning off specific functional blocks.

Writing a different pattern to the control register is often required to exit standby mode, though it can also be carried out automatically by an external trigger or interrupt. The ADC can typically restart functioning quickly because the configuration is preserved, but a brief wake-up period is frequently needed for internal voltages and clocks to normalize.

Use Cases for Standby Mode

Battery-Powered Devices: It's critical to preserve battery life in battery-powered devices, such as wearable health monitors. When no measurements are needed, the ADC can remain in standby mode, only waking up to take periodic samples.

Thermal Management: In systems with thermal restrictions, using standby mode when idle can help regulate heat dissipation.

Power Budgeting in Embedded Systems: The careful use of standby mode for the ADC when not in use can help free up power resources for other system components in embedded systems where power resources are shared among numerous components.

Remote Sensing Applications: In remote sensing applications where the system is expected to run for lengthy periods of time without maintenance, power conservation through standby mode is essential.

Power Down Modes

ADC power management is not complete without power-down modes, especially in systems where power consumption needs to be kept to a minimum for a longer length of time. This section explores the fundamental ideas behind power-down modes, compares them to standby modes, and goes over the procedures for entering and exiting power-down modes.

Basic Concepts of Power Down Mode

An ADC is placed in power-down mode, also known as deep sleep mode, to reduce power usage to the absolute minimum. The internal circuits and operations of the ADC, including the clocks and bias currents, are entirely disabled in this mode. When the ADC is not anticipated to perform any conversions for an extended period of time and power conservation is of the utmost importance, power down mode is typically employed.

Differences Between Power Down and Standby Modes

Although power down and standby modes are both used to save power, they differ significantly in several important ways:

Power Consumption: Power-down mode often uses a lot less energy than standby mode. Nearly all internal circuits are shut in power-down mode, whereas some are only partially powered in standby mode.

Wake-up Time: Compared to standby mode, power-down mode necessitates a more thorough shutdown of the ADC's internal circuits, resulting in a wake-up time that is typically longer.

State Retention: In standby mode, the ADC maintains its configuration and settings, ensuring that they are retained. However, in power-down mode, the configuration may be lost, requiring the ADC to be reconfigured when it wakes up from this state.

Use Cases: Power-down mode is used for prolonged periods of inactivity when minimal power consumption is the main issue, as opposed to standby mode, which is frequently utilized for brief periods of inactivity where a speedy restart is required.

Entering and Exiting Power Down Mode

Typically, writing particular values to control registers within the ADC is required to enter power-down mode. By doing so, the ADC gets prompted to stop using its internal clocks, bias currents, and other features. Different levels of power saving may be possible with some ADCs' numerous power-down modes.

Re-enabling the disabled functionality is required to exit power-down mode. This can be accomplished either by writing particular values to the control registers or, in some circumstances, by using an outside trigger or interrupt. Allowing enough time for the ADC's internal circuits to settle is essential while coming out of power-down mode. Furthermore, if the ADC loses its configuration while in power-down mode, it must be reconfigured.

Peak and Average Power

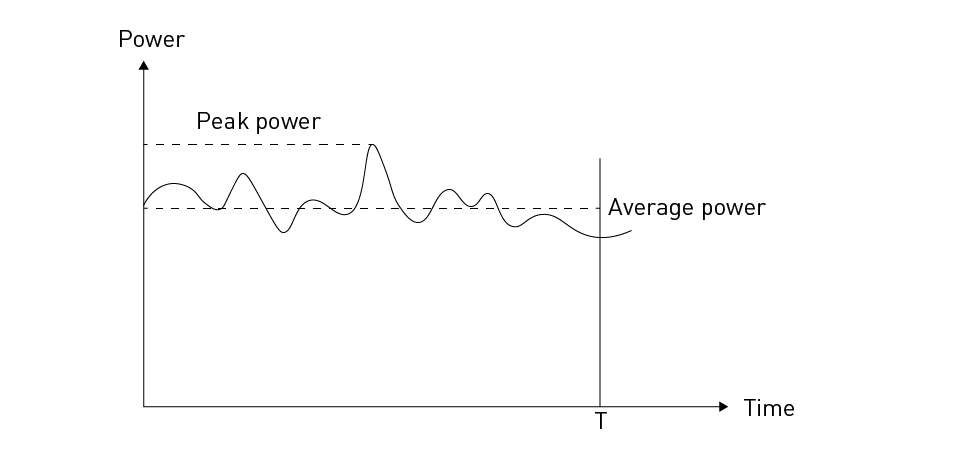

Figure 6: Peak power vs. average power

The ideas of peak and average power are essential to ADC power control. Both of these offer various viewpoints on how much energy an ADC consumes and are useful for designing systems that are optimized for performance, efficiency, or a combination of the two. The definitions of peak and average power, as well as their variations, management, and monitoring, are covered in this section.

Definitions and Differences

Peak Power: The maximum amount of power an ADC may use while operating is referred to as peak power. This typically happens when there is a lot going on, like when the ADC is processing at its greatest sample rate or when it is first starting up. Peak power is crucial for designing the system's power supply and thermal management since both the power supply and the system's ability to dissipate generated heat must be able to deliver the required peak power without interruption.

Average Power: The ADC's typical power consumption over a given time period is known as average power. It accounts for both the ADC's active and idle states. Average Power is specifically important in battery-operated systems where the lifespan of the battery is decided by how much energy is utilized on average.

Time frame is the main distinction between peak and average power. Peak power is a momentary measurement taken when the ADC is operating at full capacity. On the other hand, average power refers to the measurement of power consumption over an extended period, taking into account the complete operational cycle of the ADC. This includes both the active state when the ADC is performing its intended functions, as well as the idle state when it is not actively processing data.

Monitoring and Managing Peak and Average Power

Monitoring:

Peak Power: Peak power can be observed using an oscilloscope or a high-speed data gathering system. When the ADC is operating, the power rails can be observed to determine when power usage peaks.

Average Power: To track average power over the specified time period, a power meter or an integrating power analyzer can be employed. In order to calculate the average power, the entire amount of energy utilized throughout the time period is measured and divided by the time.

Management:

Peak Power Management: This process entails making sure the system is capable of handling the ADC's highest power requirements. Incorporating current-limiting circuitry, using a power supply with enough capacity, or using active cooling systems for thermal management are a few examples of how to achieve this.

Average Power Management: Managing average power often entails maximizing the duty cycle of the ADC. The ADC's sampling rate and power consumption can be changed in real-time based on system demands using techniques like dynamic power scaling. During idle times, using low-power modes like standby or power-down minimizes average power use.

Dynamic Power Scaling

Analog-to-Digital Converters (ADCs) power management strategies must include dynamic power scaling (DPS). It entails dynamically adjusting the ADC's power consumption in response to shifting workloads and operating needs. The approaches for decreasing dynamic power will be covered in detail in this section, with an emphasis on Adaptive Voltage Scaling (AVS), a key DPS technique.

Techniques for Reducing Dynamic Power

Dynamic Voltage Scaling (DVS): Depending on the workload at any given time, DVS adjusts the supply voltage of the ADC. By decreasing the supply voltage during times of lower activity, power consumption is decreased. However, since lowering the voltage can also lower the highest achievable speed, this typically comes at the expense of decreased performance.

Dynamic Frequency Scaling (DFS): Real-time ADC clock frequency adjustment is required for DFS. This is carried out in reaction to shifts in workload, much like DVS. The dynamic power consumption can be decreased by lowering the clock frequency when there is less activity. Combining DVS with DFS is common because lowering voltage enables lower frequencies without compromising stability.

Variable Resolution: Some ADCs permit various resolutions. Reducing the resolution allows the ADC to perform more quickly and efficiently. When high precision is not necessary, this is advantageous.

Dynamic Component Disabling: Not every ADC component needs to be on at all times in some systems. The ADC's inactive components can be selectively disabled to reduce power consumption.

Adaptive Voltage Scaling (AVS)

Dynamic Voltage Scaling (DVS) has been improved into Adaptive Voltage Scaling (AVS). While DVS normally uses preset voltage levels connected to predetermined operating frequencies, AVS more easily adjusts to the current circumstances.

Working Principle: AVS includes dynamically altering the supply voltage to satisfy performance needs while simultaneously monitoring the ADC's performance in real time. The AVS system for example can lower the voltage to conserve power if the ADC processes fewer samples per second. To guarantee performance goals are reached, the voltage can be raised when the workload is higher.

Advantages: Since AVS enables more precise voltage level control than conventional DVS, it may be more effective. It can respond to variations in workload and temperature to continually optimize power consumption.

Implementation: In order to use AVS, extra parts are typically needed, such as voltage regulators with programmable outputs and performance sensors. Additionally, choices about voltage adjustments are made using control algorithms, which can be implemented in hardware or software.

Power Management Techniques

ADC design must include power management because it is essential for minimizing power usage and guaranteeing that performance standards are satisfied. Clock gating, Power gating, and Dynamic Frequency Scaling are the three main power management strategies covered in this section.

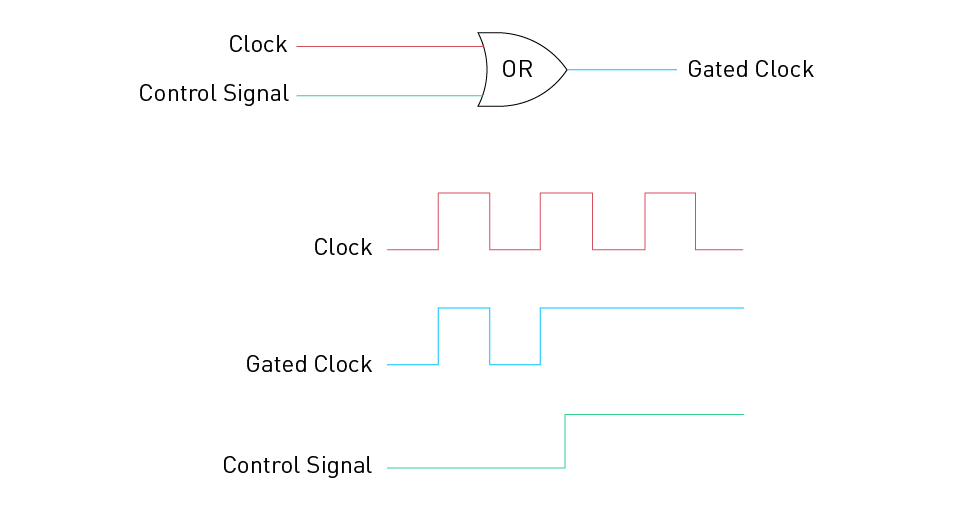

Clock Gating

Definition: Clock gating is a technique that lowers the dynamic power consumption of an ADC circuit by selectively turning off the clock signal to its inactive parts. Because dynamic power usage is related to clock frequency, shutting off the clock in some circuit components effectively lowers the power used by those components.

Implementation: To implement clock gating, extra logic gates (such as AND or OR gates) must be added to the clocking network. The operation of these gates determines if the clock signal may reach particular areas of the circuit.

Figure 7: Glock gating

Use Cases: ADCs with several processing units or components that are not required to function synchronously or constantly benefit the most from clock gating. Clock gating, for instance, can gate the clock to the filter in ADCs equipped with digital filters when filtering is not necessary.

Power Gating

Definition: Power Gating is a method for decreasing leakage power by switching off the power supply to unused areas of an ADC circuit. Switches, often transistors, are inserted between the power source and the components to do this.

Implementation: Power Gating needs to be carefully designed because the circuitry can't be activated again until the power is restored. Before a circuit is turned off, the state can be preserved using methods like retention registers, and power switches can be managed by special control circuits.

Use Cases: Power gating is particularly useful in ADCs when components are inactive for long periods of time or in low-power applications where leakage power accounts for a sizeable portion of the total power usage.

Dynamic Frequency Scaling

Definition: According to the needs of the workload, Dynamic Frequency Scaling (DFS) modifies the operational frequency of the ADC in real-time. It is very successful at lowering dynamic power usage.

Implementation: The use of Phase-Locked Loops (PLLs) or modification of the divider value in the clock generation circuit can be used to implement DFS. Modern ADCs could include modules that make DFS easier

Use Cases: DFS is advantageous in situations where the workload of the ADC changes over time, such as in sensor data acquisition systems where the sample rate may dynamically vary.

直接登录

创建新帐号