AN222 - MP5048 并联应用设计

每月为您发送最具参考价值的行业文章

我们会保障您的隐私

简介

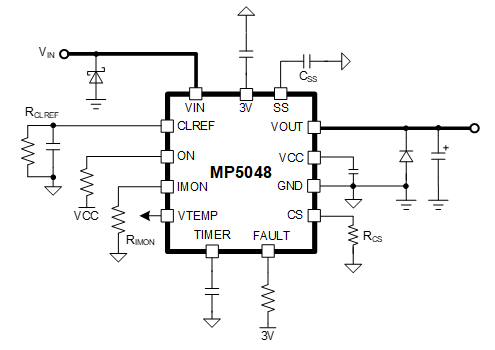

本应用说明将讨论MP5048 的并联应用设计。MP5048是一款单片集成控制器和开关,可并联应用于大电流应用。该器件内置一个上管MOSFET (HS-FET) ,以及让它能够作为独立器件运行或由热插拔控制器控制的相关电路。每个 MP5048 器件都可驱动高达 15A 的连续电流。图 1 显示了单个 MP5048 器件的典型应用原理图。

图1: MP5048典型独立应用原理图

当一个电路卡插入带电背板电源时,MP5048 能够限制负载上的浪涌电流,从而限制背板上的压降。它还通过限流参考输入控制栅极电压,从而实现内部 MOSFET 限流。

MP5048 提供了多种可简化系统设计的功能,其中包括用于监控输出电流 (IOUT) 和芯片温度的集成解决方案,所以它无需外部电流采样功率电阻、功率 MOSFET 或温度采样。此外,它还可以检测功率 FET 栅源和漏极的短路情况,并向控制器提供反馈。

并联应用

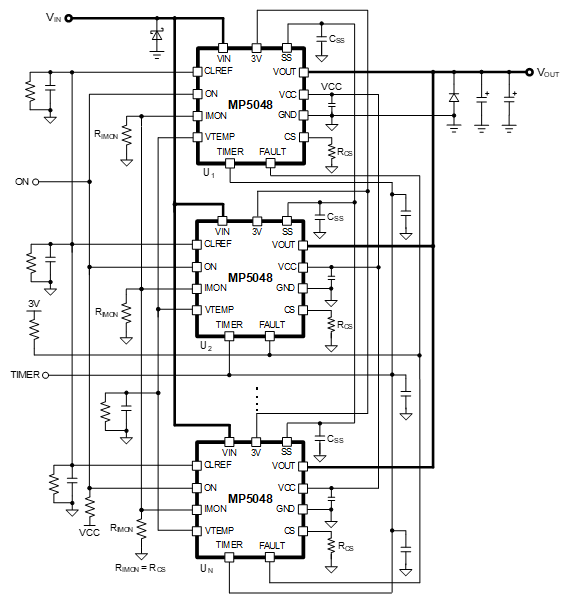

MP5048 可以并联应用以提供超过 15A 限制的电流。图 2 显示了多个 MP5048 器件并联的典型应用示意图。

图2: MP5048并联应用典型原理图

表 1 显示了实现正常功能必要的引脚连接。每个 CS 引脚都必须连接一个单独的电阻,并不能连接在一起,而且所有CS 电阻必须具有相同的阻值。

表 1 显示了并联应用中必须连接在一起的 MP5048 引脚。

表1: 并联应用中必要的引脚连接

| 引脚名称 | 必要的引脚连接 |

| CLREF | 根据 CLREF 引脚的标称电压 (VCLREF_NORM) 和电流限制 (ILIMIT),在每相放置一个电阻。VCLREF_NORM 可以通过公式 (1) 计算:

$$V_{CLREF\_NORM} = I_{CLREF\_NORM} \times R_{CLREF}$$ 其中 ICREF_NORM 是 CLREF 标称电流,RCLREF 是CLREF 电阻。 ILIMIT 可以使用公式 (2) 计算: $$I_{LIMIT} = \frac {V_{CLREF\_NORM}}{(g_{CS} \times R_{CS})}$$ 其中 gCS 是功率 FET 完全导通时的电流采样增益(通常为 25µA/A),RCS 是 CS 电阻。 除此之外,需要在 CLREF 和 AGND 之间放置一个 1nF 至10nF 的电容。 |

| ON | 所有并联的 MP5048 器件必须将 ON 引脚连接在一起,以确保使能信号相同。该信号可以来自逻辑设备,也可以来自 VIN 和 ON 引脚之间的电阻分压器。 |

| IMON | IMON 引脚提供运行期间的总电流,该电流可通过公式 (3) 计算:

$$\text{总电流} = N \times \text{电熔丝}$$

启动期间,IMON 可平衡 MP5048 器件之间的软启动 (SS) 电流。在每相放置一个电阻。有关RCS 计算的更多详情,请参阅 MP5048 数据手册。

等效 IMON 电阻 (RIMON) 可通过公式 (4) 计算: $$R_{IMON} = \frac{R_{cs}} {N}$$ 其中 N 为并联的器件数量。 |

| GND | 每个 MP5048 器件的 GND 引脚都必须连接至相同的接地参考。 |

| VIN | VIN 引脚是电熔丝器件的高压 (HV) 输入。所有并联的 MP5048 器件必须连接到同一电源平面。它还需要一个TVS 保护器件来防止输入电压 (VIN) 超过 MP5048 数据手册中规定的限值。 |

| SS | 在每相的 SS 引脚和模拟信号地之间放置一个电容,以确保在启动序列中的软启动同步。 |

| VOUT | 所有并联连接的 MP5048 器件 VOUT 引脚都必须连接到同一电源平面。VOUT 和 GND 引脚之间还需要连接一个肖特基二极管,以在过流保护 (OCP) 或短路保护 (SCP) 条件下提供大电流续流路径。 |

| TIMER | 在每相的 TIMER 引脚和模拟信号地之间放置一个电容。TIMER 用于同步所有并联器件的插入延迟、重试延迟和 OCP 定时器。 |

表2显示了可独立或连接在一起的MP5048可选引脚连接。

表2: 可选引脚连接

| 引脚名称 | 可选引脚连接 |

| VTEMP | 在 VTEMP 和模拟信号地之间放置一个最小 10kΩ 的电阻和一个最大 1nF 的电容。所有 MP5048 器件的 VTEMP 引脚可以连接在一起以获取最高的器件读数,也可以路由每个单独的信号以读取每个电熔丝的温度。 |

| VCC | 在每相的 VCC 和模拟信号地之间放置 1µF 电容。所有电熔丝的 VCC 引脚可以连接在一起,也可以提供单独连接。 |

| 3V | 在每相的 3V 和模拟信号地之间放置一个 1µF 电容。所有相位的 3V 引脚可以连接在一起,也可以提供单独连接。 |

| FAULT | FAULT 引脚提供开漏输出,可以通过 FAULT 和 VCC 之间或 FAULT 和 3V 之间的 10kΩ 至 100kΩ 电容上拉该输出,具体取决于系统所需的电压水平。FAULT 可以作为单独的连接保留,以提供详细的电熔丝故障监控,也可以连接在一起以获得所有电熔丝器件的组合故障信号。 |

| MODE | 通过MODE引脚,可将故障条件下的电熔丝操作设置为打嗝模式或闭锁模式。所有 MP5048 器件的 MODE 引脚均可单独设置,但并联连接的所有MP5048 器件必须具有相同的 MODE 设置。MODE 引脚也可连接在一起以设置器件的操作。 |

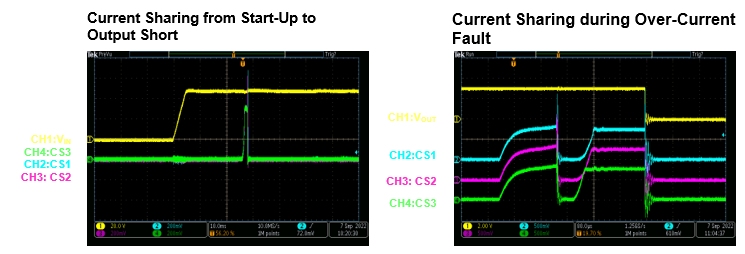

在启动过程中,SS 和 IMON 引脚之间的连接可以实现并联 MP5048 器件之间的电流平衡。SS 引脚可确保所有并联 MP5048 器件在启动序列期间具有相同的软启动 (SS) 斜率,这样可在输出电压 (VOUT)上升时在 MP5048 器件之间提供固有的电流平衡。如果意外情况导致其中一个 MP5048 器件的电流增大,则来自 IMON 的总电流和通过 CS 引脚的独立电熔丝电流将激活主动电流平衡环路,从而平衡并联 MP5048 器件之间的电流。

除了布局之外,MOSFET 电阻 (RDS(ON))的正温度系数也有助于实现电流平衡。如果一个 MP5048 器件承载了更多的电流,则该器件会升温更多,并提高其 RDS(ON),这会迫使电流流向其他的 MP5048 器件。

如果发生过载情况,并联的 MP5048 器件会调节至已配置好的过流保护 (OCP) 阈值,而且连接的 TIMER 引脚开始充电。一旦 TIMER 引脚上的电压达到跳闸阈值 (0.6V),所有 MP5048 器件都会因过流 (OC) 而被禁用并关断。如果 MP5048 器件被设置为闭锁模式,则可通过以下两种方法来清除故障。MP5048 保持故障状态直到 ON 引脚上的电源循环为低电平然后再变为高电平,此时清除故障条件并开始 SS 导通序列。要清除故障并执行全面的器件复位,可将输入电压 (VIN) 降至 3V 以下,并持续 100ms以触发 VCC 电压 (VCC) 欠压锁定 (UVLO) 下降阈值;这样就可实现全面器件复位,并在 VIN 上升时插入延迟。

在一次电源循环中,如果 VIN 未在 100ms 内降至 3V 以下,则不会触发所有并联 MP5048 器件的 VCC UVLO 下降阈值。这样,触发了 VCC UVLO 下降阈值的 MP5048 器件进入初始化模式,而未触发的则保持正常运行。如果 MP5048 器件处于不同的运行状态,则并联的 MP5048器件将无法正确重启。

如果 MP5048 器件被设置为打嗝模式,则 TIMER 会在所有并联的 MP5048 器件中安排重试时间。在重试时间结束时,并联MP5048 设备将被重启,并开始新的启动序列。

为防止上电复位 (POR),正常运行期间的 VIN 必须超过 5.25V的欠压锁定 (UVLO) 阈值。

EV5048-V-00A 评估板

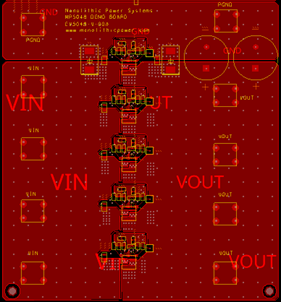

图 3 展示了5 相 EV5048-V-00A评估板。本应用说明将详细介绍 3 相 EV5048-V-00A 的测试结果。

图3: EV5048-V-00A评估板

评估板布局

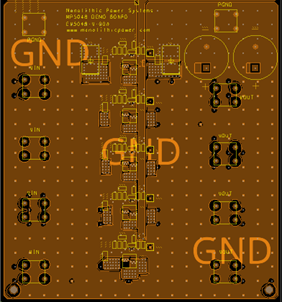

TEV5048-V-00A 评估板由四层组成(见图 4 至图 7)。每个电熔丝的顶层都具有相同的形状,以便在稳态运行期间实现所有 MP5048 器件的电流平衡。

图4: EV5048-V-00A的顶层

图5: EV5048-V-00A的中间层1

图6: EV5048-V-00A的中间层2

图7: EV5048-V-00A的底层

评估板原理图

图8显示了EV5048-V-00A评估板的电熔丝原理图。

图8: EV5048-V-00A电熔丝原理图

波形

结语

本应用说明介绍了实现MP5048稳定并联运行的简单系统设计。并联应用的电熔丝设计可以提供极大的灵活性,满足日益增长的大电流电路保护需求。MP5048 提供了一种多功能的解决方案,它提供了重要的引脚连接以及正温度系数,能够实现强大的电路保护以及大电流并联运行中的电流平衡。

_______________________

您感兴趣吗?点击订阅,我们将每月为您发送最具价值的资讯!

技术论坛

Latest activity a year ago

Latest activity a year ago

11 回复

11 回复

Latest activity a year ago

Latest activity a year ago

24 回复

24 回复

Latest activity a year ago

Latest activity a year ago

17 回复

17 回复

直接登录

创建新帐号